Sign In / Sign Out

Navigation for Entire University

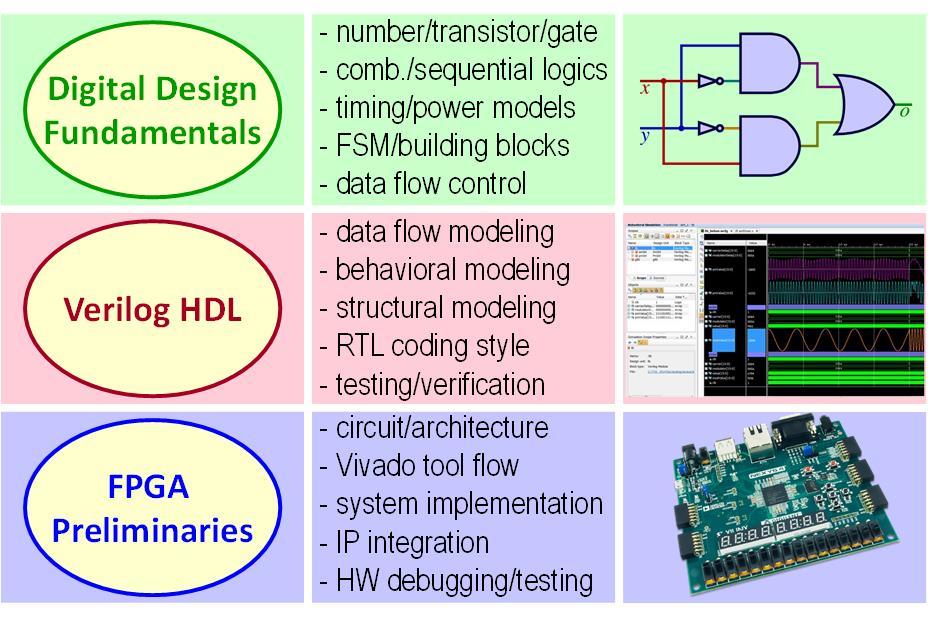

This course focuses on fundamental concepts for designing and implementing digital circuits and systems on field-programmable gate array (FPGA). Topics include number systems and formats, boolean algebra, CMOS transistor, logic gates, power, combinational and sequential logic, finite state machine, timing, Verilog HDL, arithmetic units, memories, data flow control, and FPGA technology.

An important objective of the course is to equip and provide students with the necessary skills and abundant hands-on experience in dealing with digital circuits and systems in real hardware. For this purpose, the Nexys™4 DDR Artix-7 FPGA Boards and Xilinx Vivado Design Suite will be employed in tutorials, lab assignments, and class projects.

Spring 2020

Fall 2018

Fall 2017

Fall 2016

Fall 2015

Copyright © 2015-2024 Parallel Systems and Computing Laboratory. All right reserved. | Site Admin: Fengbo Ren | Powered by Drupal.