UNIVERSITY OF CALIFORNIA Los Angeles

# A Scalable VLSI Architecture for Real-Time and Energy-Efficient Sparse Approximation in Compressive Sensing Systems

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical Engineering

by

Fengbo Ren

2015

© Copyright by Fengbo Ren 2015

### Abstract of the Dissertation

# A Scalable VLSI Architecture for Real-Time and Energy-Efficient Sparse Approximation in Compressive Sensing Systems

by

#### Fengbo Ren

Doctor of Philosophy in Electrical Engineering University of California, Los Angeles, 2015 Professor Dejan Marković, Chair

Digital electronic industry today relies on Nyquist sampling theorem, which requires to double the size (sampling rate) of the signal representation on the Fourier basis to avoid information loss. However, most natural signals have very sparse representations on some other orthogonal (non-Fourier) basis. This mismatch implies a large redundancy in Nyquist-sampled data, making compression a necessity prior to storage or transmission. Recent advances in compressive sensing (CS) theory offer us an alternative data acquisition framework, which can greatly impact power-starved applications such as wireless sensors. CS techniques provide a universal approach to sample compressible signals at a rate significantly below the Nyquist rate with limited information loss. Therefore, CS is a promising technology for realizing configurable, cost-effective, miniaturized, and ultra-low-power data acquisition devices for mobile and wearable applications.

However, the digital signal processing of compressively-sampled data involves solving a sparse approximation problem, which requires iterative-searching algorithms that have high computational complexity and require intensive memory access. As a result, existing software solutions are neither energy-efficient nor cost-effective for real-time processing of compressively-sampled data, especially when the processing is to be performed on energylimited devices. To solve this problem, this dissertation presents a scalable VLSI architecture that can be implemented on field-programmable gate arrays (FPGAs) or system-on-chips (SoCs) to perform dedicated-hardware-driven sparse approximation. A VLSI soft-IP core of the sparse approximation engine is developed in Verilog-HDL, which supports a floating-point data format with 10 design parameters, providing a high dynamic range and the flexibility for application-specific user customizations. Taking advantage of the algorithm-architecture co-design that leverages algorithm reformulations, configurable architectures, and efficient memory mapping schemes, the proposed VLSI architecture features a 100% utilization of the computing resources and is scalable in terms of computation parallelism and memory capability.

The hardware emulation of the soft-IP core on a 28-nm Xilinx Kintex-7 FPGA shows that our design achieves the same level of accuracy as the double-precision C program running on an Intel Core i7-4700MQ mobile processor, while providing  $47-147 \times$  speed-up for ECG signal reconstruction. Furthermore, a 12–237 KS/s 12.8 mW sparse approximation engine chip is realized in a 40-nm CMOS technology for enabling the mobile data aggregation of compressively sampled biomedical signals in CS-based wireless health monitoring systems. The measurement results show that the sparse approximation engine chip operating at the minimum energy point achieves a real-time throughput for reconstructing 61–237 channels of biomedical signals simultaneously with < 1% of a mobile device's 2W power budget, which is  $14,100 \times$  more energy-efficient than the software solver running on the CPU. For high-sparsity signal reconstruction, the sparse approximation engine chip is  $76-350 \times$  more energy-efficient than prior hardware designs. With a <1% power budget of a mobile device, the  $5.13 \text{ mm}^2$  sparse approximation engine chip integrated in 40-nm CMOS can enable a  $2-3\times$  energy saving at CS-based sensor nodes while providing timely feedback and bringing signal intelligence closer to the user, presenting a significant advantage for 24/7 wireless health monitoring.

The dissertation of Fengbo Ren is approved.

Miloš D. Ercegovac Babak Daneshrad William J. Kaiser

Dejan Marković, Committee Chair

University of California, Los Angeles

2015

To my parents, and my wife.

# TABLE OF CONTENTS

| 1        | Intr          | oducti | on                                                                             | 1  |

|----------|---------------|--------|--------------------------------------------------------------------------------|----|

|          | 1.1           | Backg  | round and Scope of The Dissertation                                            | 1  |

|          | 1.2           | CS-bas | sed Wireless Health Monitoring                                                 | 3  |

|          | 1.3           | Disser | tation Outline                                                                 | 6  |

| <b>2</b> | Spa           | rse Ap | oproximation (SA)                                                              | 8  |

|          | 2.1           | Prelim | linary                                                                         | 8  |

|          |               | 2.1.1  | Notation                                                                       | 8  |

|          |               | 2.1.2  | $\ell_p$ Norm                                                                  | 9  |

|          |               | 2.1.3  | Signal Sparsity                                                                | 10 |

|          | 2.2           | Proble | em Definition                                                                  | 13 |

|          | 2.3           | Applic | eations of SA                                                                  | 14 |

|          |               | 2.3.1  | Compressive Sensing (CS)                                                       | 14 |

|          |               | 2.3.2  | Sparse Representation Based Classification (SRC) $\ldots \ldots \ldots \ldots$ | 20 |

|          |               | 2.3.3  | Signal Denoising                                                               | 22 |

|          |               | 2.3.4  | Data Separation                                                                | 22 |

| 3        | $\mathbf{SA}$ | Algori | ${ m thms}$                                                                    | 25 |

|          | 3.1           | Hardw  | vare-Friendly Algorithms                                                       | 26 |

|          |               | 3.1.1  | Orthogonal Matching Pursuit (OMP)                                              | 26 |

|          |               | 3.1.2  | Homotopy                                                                       | 27 |

|          |               | 3.1.3  | Iterative Soft Tresholding (IST)                                               | 30 |

|          | 3.2           | Algori | thm Benchmarking                                                               | 31 |

|          |               | 3.2.1  | Experiment Setting                                                             | 32 |

|   |     | 3.2.2 Benchmarking Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3 |

|---|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 4 | Alg | orithm Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ) |

|   | 4.1 | Complexity Analysis of OMP 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ) |

|   | 4.2 | Algorithm Reformulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3 |

|   |     | 4.2.1 Square-Root-Free OMP 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3 |

|   |     | 4.2.2 Incremental Cholesky Factorization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5 |

|   |     | 4.2.3 Incremental Estimation Update                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3 |

|   |     | 4.2.4 Complexity Reduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7 |

|   | 4.3 | Hierarchical AS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ) |

| 5 | VLS | SI Architecture Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1 |

|   | 5.1 | System Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1 |

|   | 5.2 | Computation Cores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3 |

|   |     | 5.2.1 Vector Core (VC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3 |

|   |     | 5.2.2 Scalar Core (SC) $\ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3 |

|   | 5.3 | Data Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ) |

|   | 5.4 | Memory Control Scheme for Handling Cholesky Factorization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ) |

|   | 5.5 | Dynamic Configuration of System Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3 |

|   | 5.6 | Data Format for Preserving Software-Level Accuracy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7 |

|   | 5.7 | Compile-Time Scalability and Run-Time Configurability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ) |

| 6 | FP( | GA Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2 |

| 0 | 6.1 | Xilinx KC705 Hardware Evaluation Platform     72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |

|   | 6.2 | Computer-Aided Design (CAD) Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |

|   | 6.3 | Implementation Results       76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

|   | 0.0 | Impromotion toolutor a contract of the contrac | , |

|    | 6.4    | Bench   | marking Study                             | . 79  |

|----|--------|---------|-------------------------------------------|-------|

|    |        | 6.4.1   | Testing Environment                       | . 79  |

|    |        | 6.4.2   | Accuracy Benchmarking                     | . 80  |

|    |        | 6.4.3   | Performance Benchmarking                  | . 84  |

| 7  | AS.    | A Eng   | gine Chip for Mobile ExG Data Aggregation | . 88  |

|    | 7.1    | Chip I  | Design                                    | . 88  |

|    | 7.2    | Chip 7  | Testing Environment                       | . 92  |

|    | 7.3    | Chip N  | Measurement Results                       | . 95  |

| 8  | Con    | clusior | <b>n</b>                                  | . 101 |

|    | 8.1    | Resear  | rch Contributions                         | . 102 |

|    | 8.2    | Future  | e Work                                    | . 104 |

| Re | eferei | nces .  |                                           | . 106 |

# LIST OF FIGURES

| 1.1 | Nyquist framework                                                                                                        | 2  |

|-----|--------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | A CS-based wireless health monitoring system                                                                             | 4  |

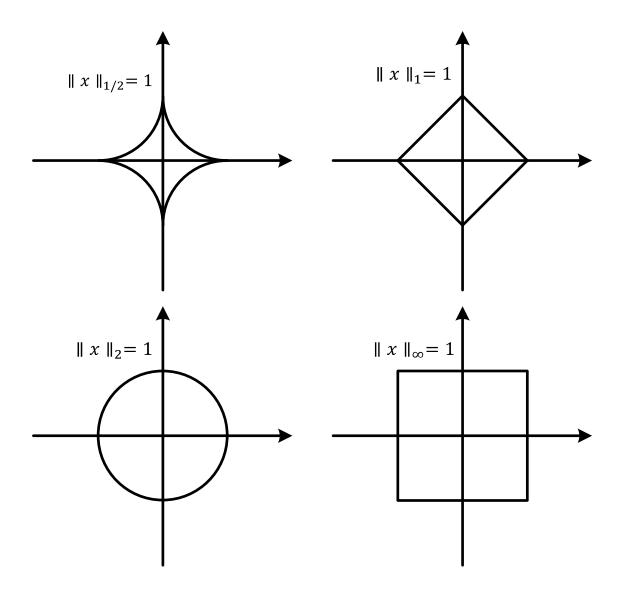

| 2.1 | Illustration of unit circles in 2-D space                                                                                | 10 |

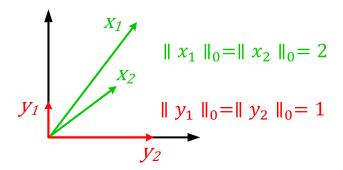

| 2.2 | Illustration of 1- and 2-sparse vectors in 2-D space                                                                     | 11 |

| 2.3 | Example of a 10-sparse signal in 100-dimensional space $x \in \mathbb{S}_{10}^{100}$                                     | 11 |

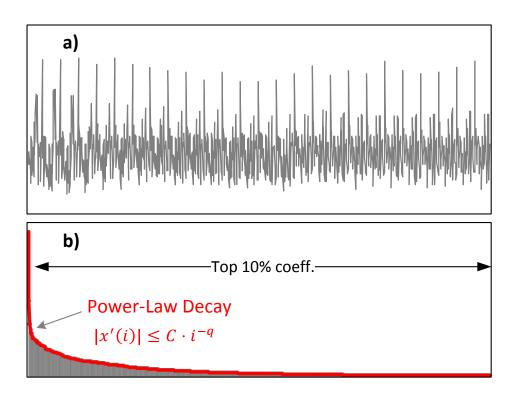

| 2.4 | Example of (a) an EEG signal and (b) its top 10% coefficients (sorted by amplitude) on the DCT basis.                    | 12 |

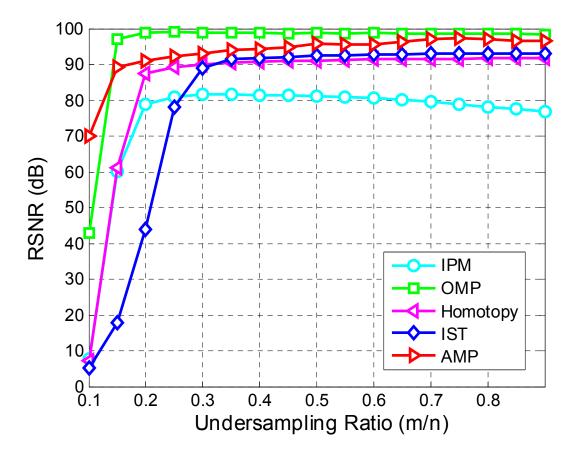

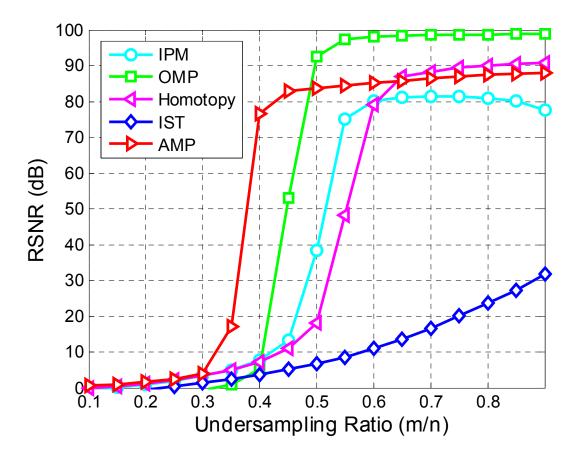

| 3.1 | RSNR performance of the SA algorithms for a high signal sparsity ratio $(k/n = 0.03)$ in the high-SNR case (SNR=100 dB). | 33 |

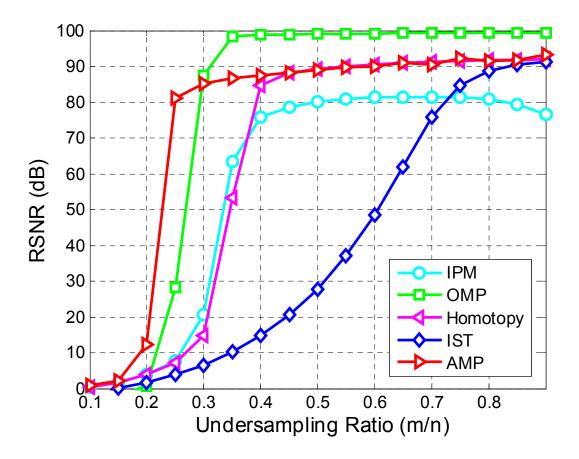

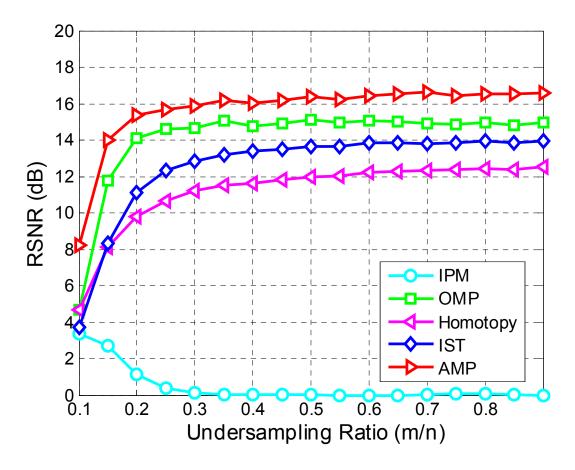

| 3.2 | RSNR performance of the SA algorithms for a medium signal sparsity ratio $(k/n = 0.1)$ in the high-SNR case (SNR=100 dB) | 34 |

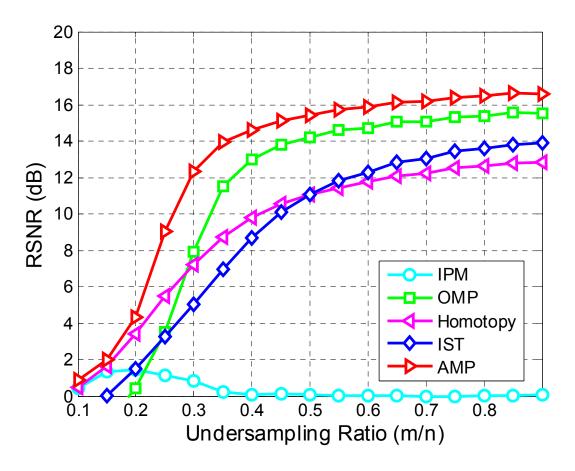

| 3.3 | RSNR performance of the SA algorithms for a low signal sparsity ratio $(k/n = 0.2)$ in the high-SNR case (SNR=100 dB).   | 35 |

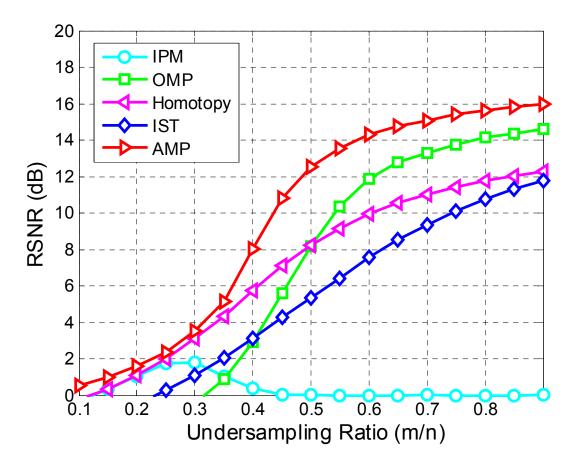

| 3.4 | RSNR performance of the SA algorithms for a high signal sparsity ratio $(k/n = 0.03)$ in the high-SNR case (SNR=20 dB).  | 36 |

| 3.5 | RSNR performance of the SA algorithms for a medium signal sparsity ratio $(k/n = 0.1)$ in the high-SNR case (SNR=20 dB). | 37 |

| 3.6 | RSNR performance of the SA algorithms for a low signal sparsity ratio $(k/n = 0.2)$ in the high-SNR case (SNR=20 dB)     | 38 |

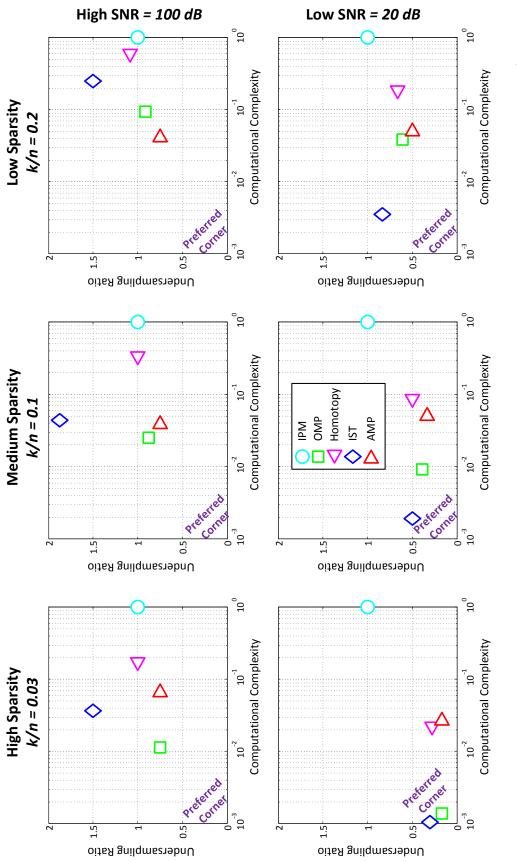

| 3.7 | Comparison of the SA algorithms on the plane of undersampling ratio versus computational complexity.                     | 39 |

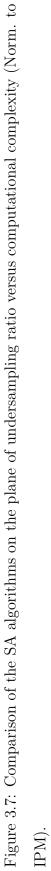

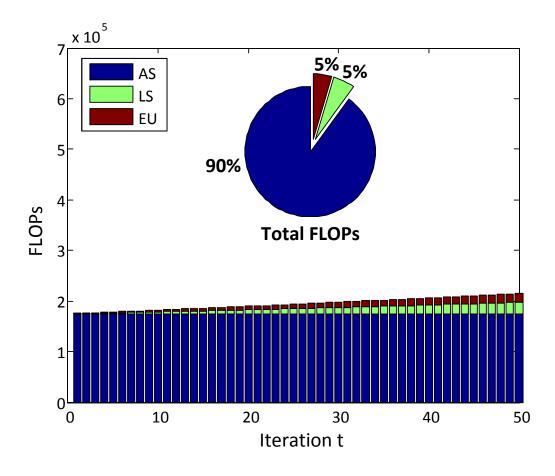

| 4.1 | Illustration of the computation breakdown of OMP $(n = 500, m = 175, k = 50).$                                           | 42 |

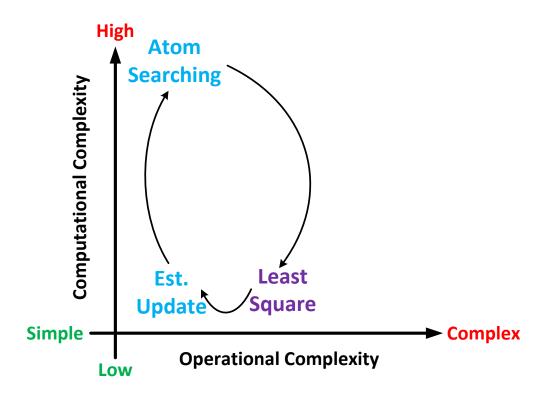

| 4.2 | Complexity characteristic of OMP.                                                                                        | 43 |

| 4.3  | Illustration of the computation breakdown of the reformulated OMP ( $n =$   |     |

|------|-----------------------------------------------------------------------------|-----|

|      | 500, m = 175, k = 50)                                                       | 50  |

| 4.4  | Complexity characteristic of the reformulated OMP                           | 51  |

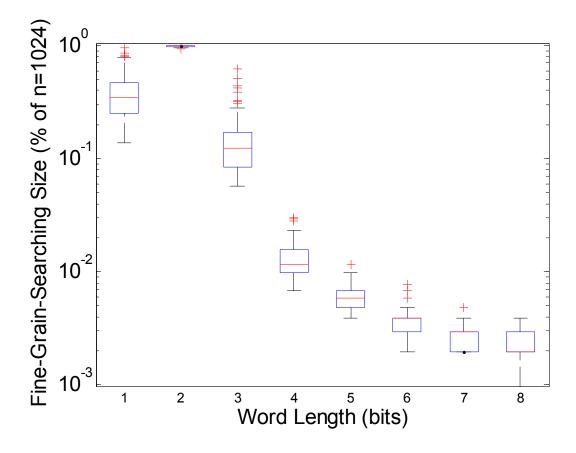

| 4.5  | Illustration of comparing two inner products using MSB only                 | 52  |

| 4.6  | The design space of the hierarchical atom searching method extracted from   |     |

|      | the reconstruction test of compressively sampled ECG signals                | 53  |

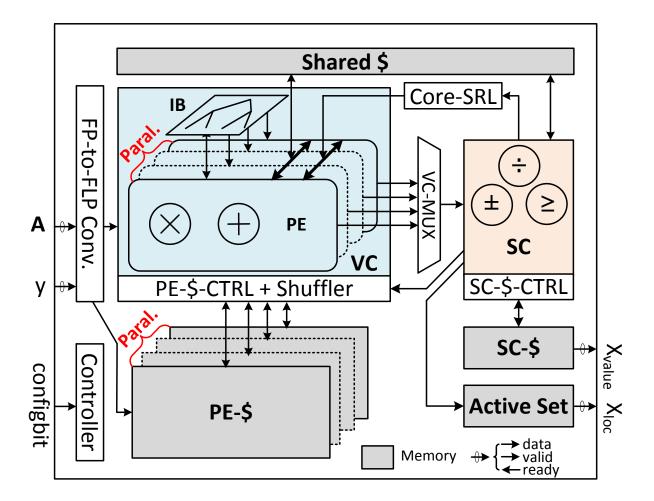

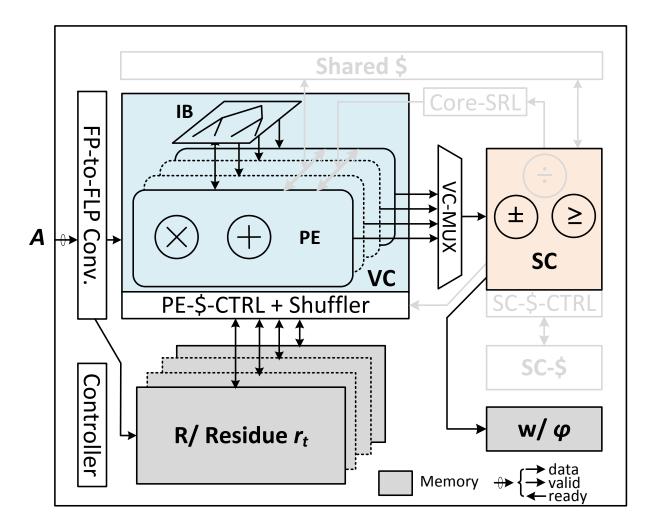

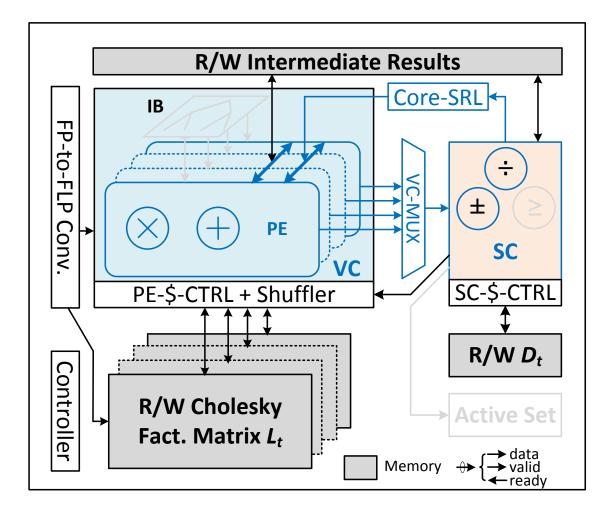

| 5.1  | System architecture of the SA engine                                        | 55  |

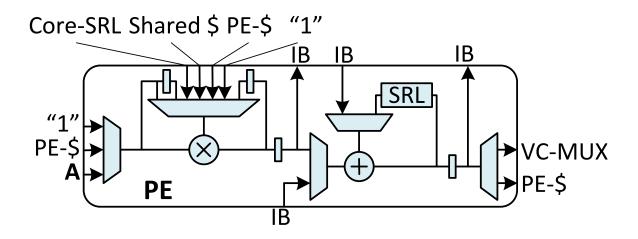

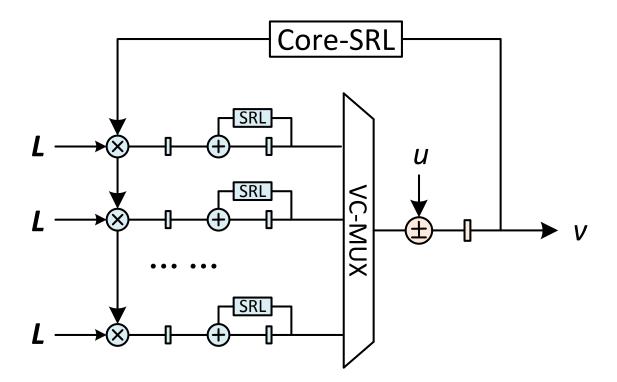

| 5.2  | Block diagram of the PE in the VC                                           | 57  |

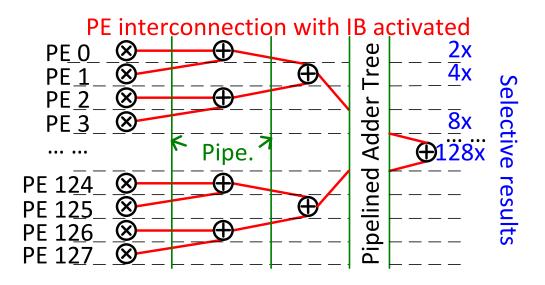

| 5.3  | PE interconnects for computing vector inner products                        | 58  |

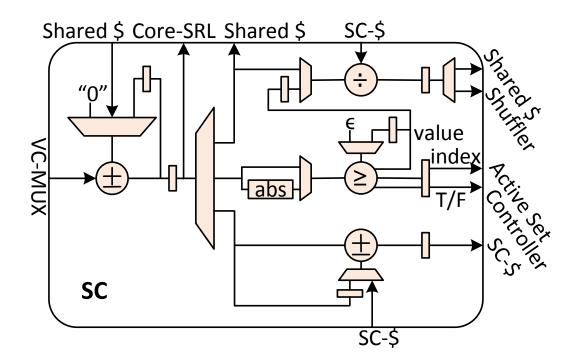

| 5.4  | Block diagram of the SC                                                     | 59  |

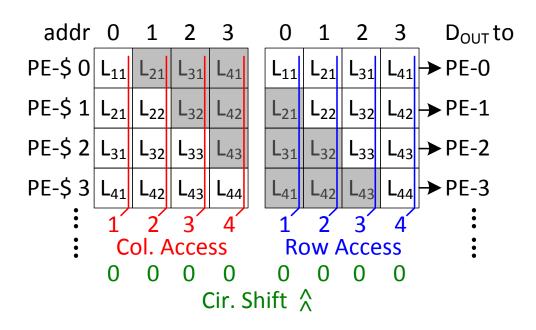

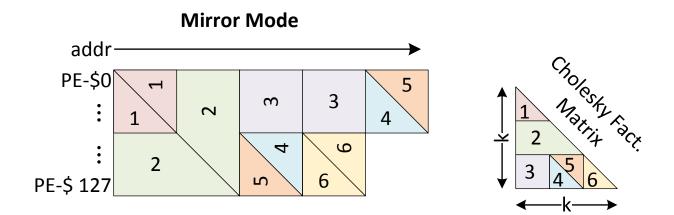

| 5.5  | Data mapping scheme of PE caches in the mirror mode for handling Cholesky   |     |

|      | factorization.                                                              | 61  |

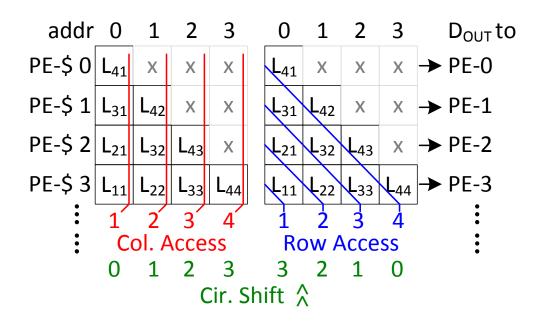

| 5.6  | Data folding scheme of PE caches in the mirror mode for handling Cholesky   |     |

|      | factorization.                                                              | 62  |

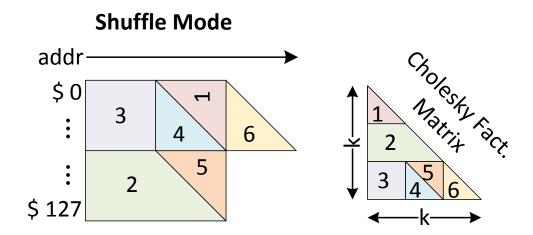

| 5.7  | Data mapping scheme of PE caches in the shuffle mode for handling Cholesky  | 60  |

|      | factorization.                                                              | 63  |

| 5.8  | Data folding scheme of PE caches in the shuffle mode for handling Cholesky  | 6.4 |

|      | factorization.                                                              | 64  |

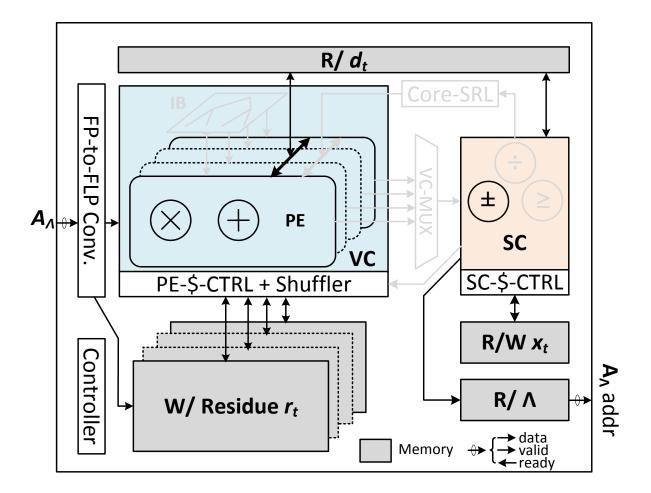

| 5.9  | Dynamic configuration of the system architecture in the AS task             | 65  |

| 5.10 | Dynamic configuration of the system architecture in the LS task             | 66  |

| 5.11 | Data-path configuration for computing FS and BS                             | 67  |

| 5.12 | Dynamic configuration of the system architecture in the EU task. $\ldots$ . | 68  |

| 5.13 | Summary of dynamic configuration scheme of the system architecture          | 69  |

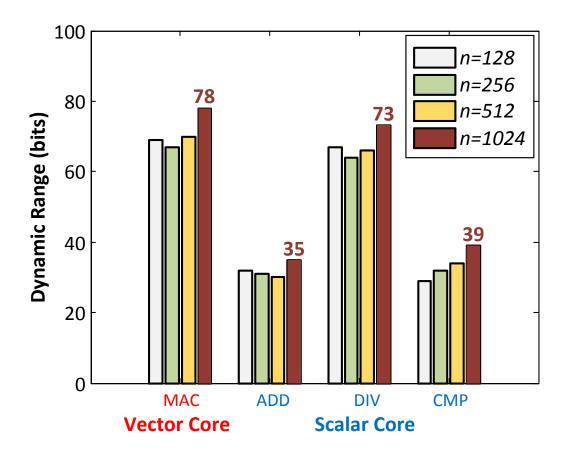

| 5.14 | Worst-case dynamic range required by hardware units to preserve the         |     |

|      | software-level accuracy for varying problem size $n$                        | 70  |

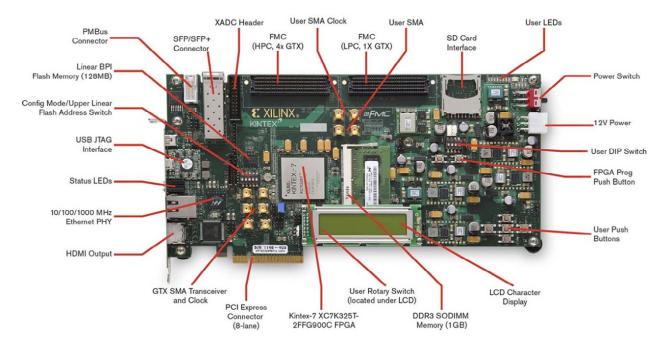

| 6.1  | Xilinx KC705 evaluation board (courtesy of Xilinx, Inc.)                                                               | 73 |

|------|------------------------------------------------------------------------------------------------------------------------|----|

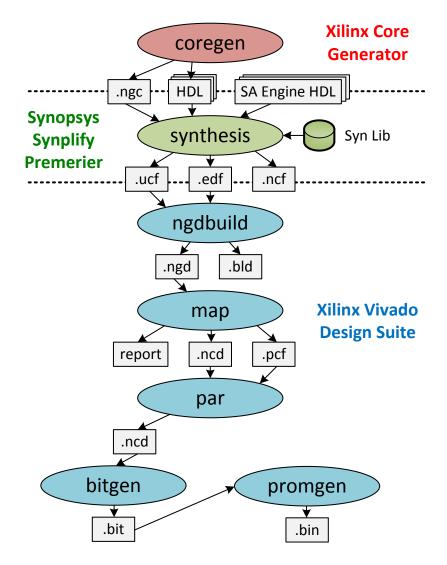

| 6.2  | CAD flows for implementing the SA engine on the KC705 platform                                                         | 75 |

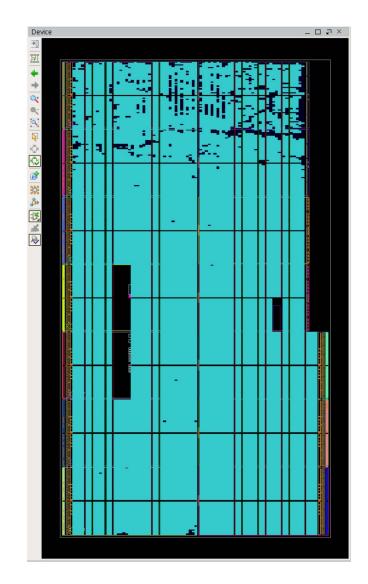

| 6.3  | Layout view of the FPGA with the SA engine implemented                                                                 | 78 |

| 6.4  | Implementation results in comparison to prior work                                                                     | 79 |

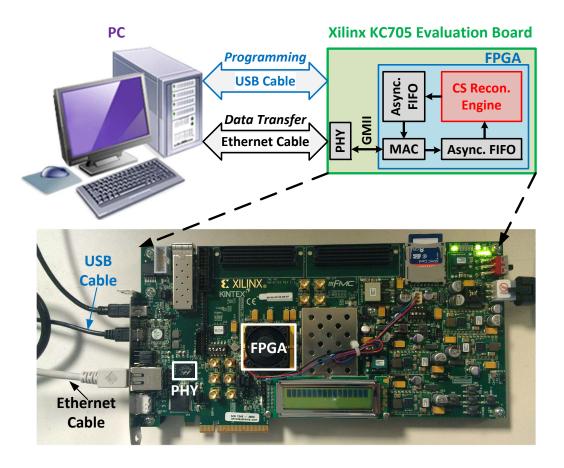

| 6.5  | Testing environment on the Xilinx KC705 evaluation platform                                                            | 80 |

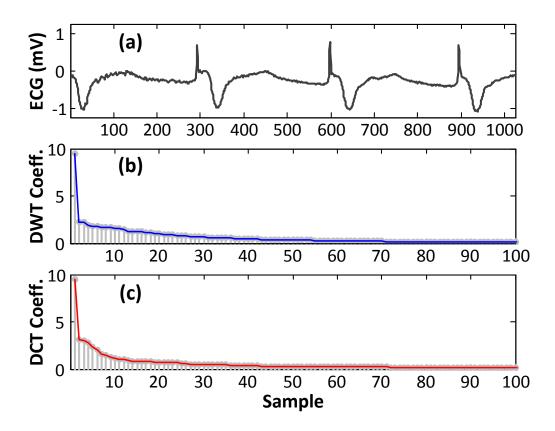

| 6.6  | An example of (a) the ECG signal from MIT-BIH database and its top 100 sorted (b) DWT and (c) DCT coefficients.        | 81 |

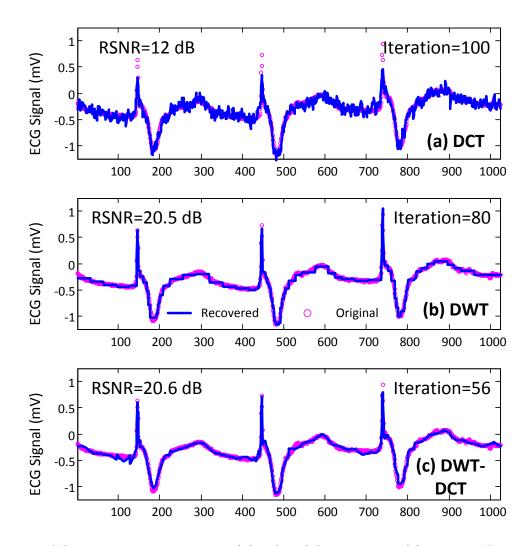

| 6.7  | ECG signal reconstructed on (a) DCT, (b) DWT, and (c) DWT-DCT joint                                                    |    |

|      | basis, respectively.                                                                                                   | 82 |

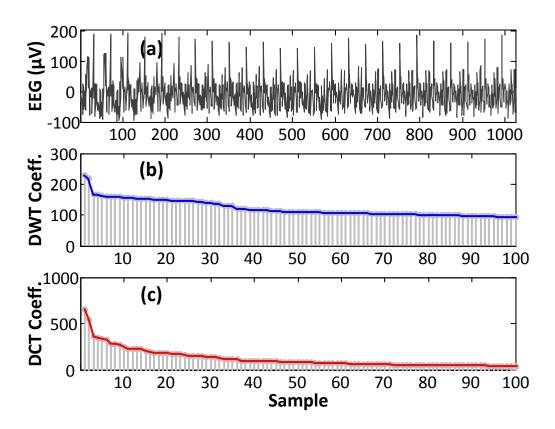

| 6.8  | An example of (a) the EEG signal from UCSD-EEGLAB database and its top<br>100 sorted (b) DWT and (c) DCT coefficients. | 83 |

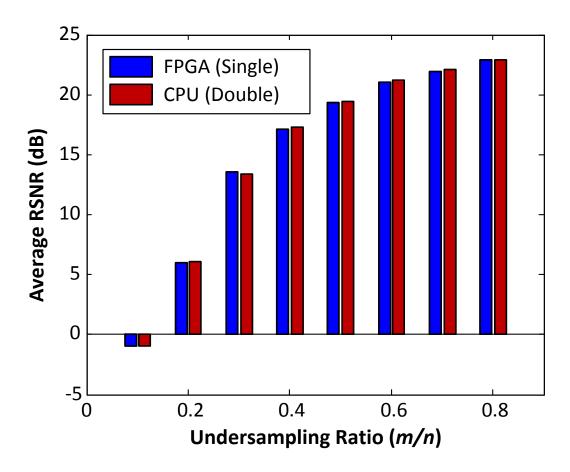

| 6.9  | Average RSNR performance measured from the ECG reconstruction in C                                                     |    |

|      | program and on the FPGA at different undersampling ratio $(m/n)$                                                       | 84 |

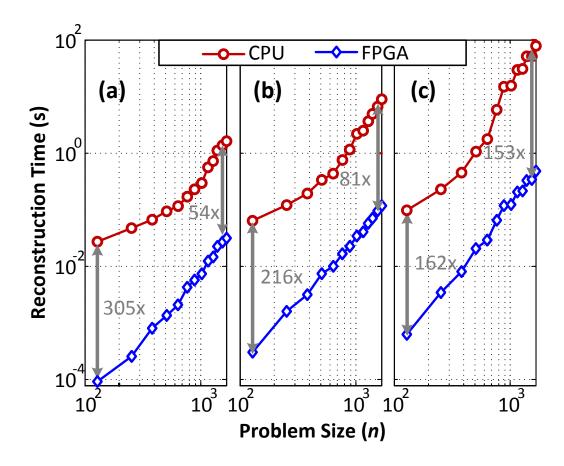

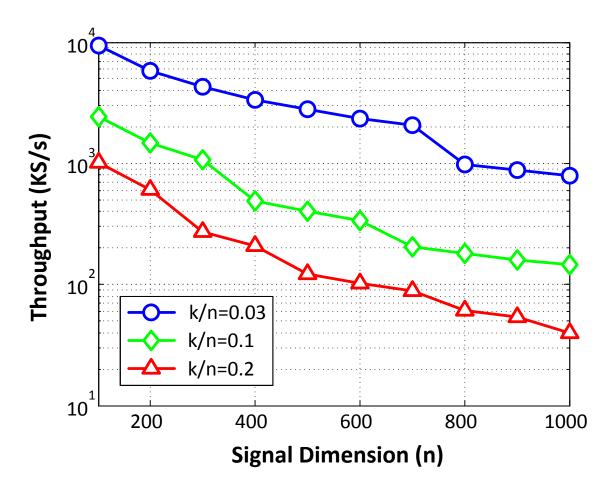

| 6.10 | Averaged FPGA reconstruction time versus CPU run time measured from the                                                |    |

|      | experiments at different problem size $n. \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                            | 85 |

| 6.11 | Reconstruction throughput of the FPGA implementation                                                                   | 87 |

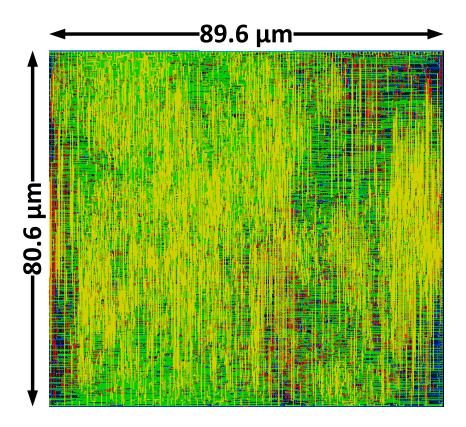

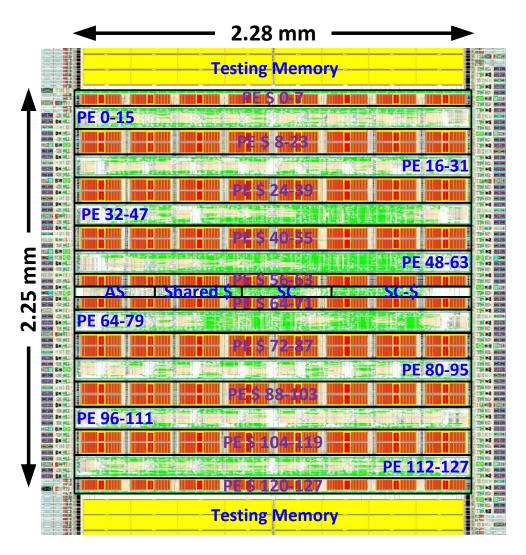

| 7.1  | Layout view of the PE block.                                                                                           | 90 |

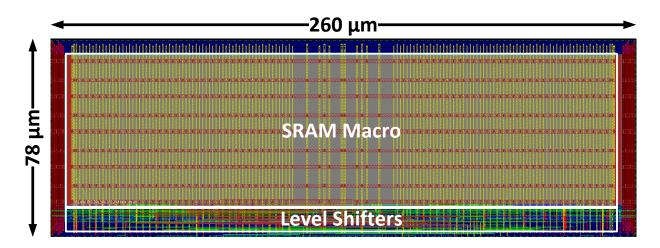

| 7.2  | Layout view of the PE cache block.                                                                                     | 91 |

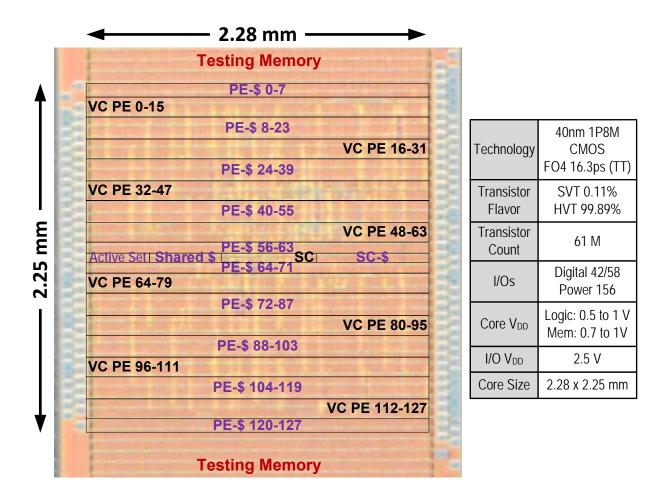

| 7.3  | Layout view of the SA engine chip                                                                                      | 92 |

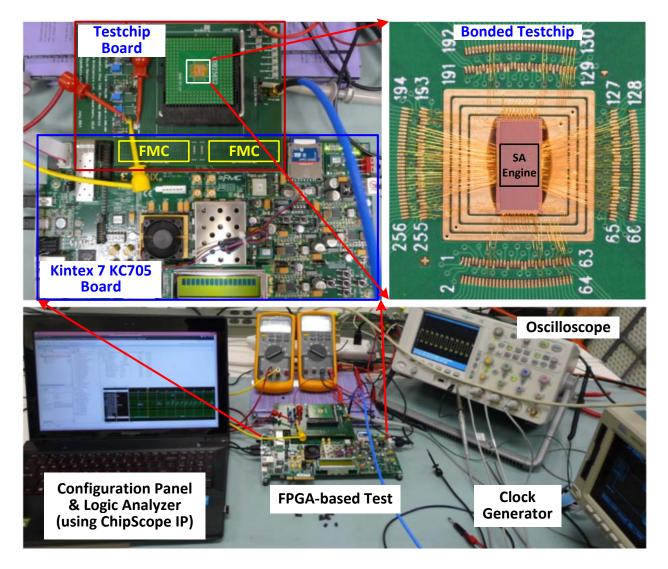

| 7.4  | Chip testing environment.                                                                                              | 93 |

| 7.5  | Customized control panel of the chip testing in the Xilinx Vivado Design Suite                                         |    |

|      | environment.                                                                                                           | 94 |

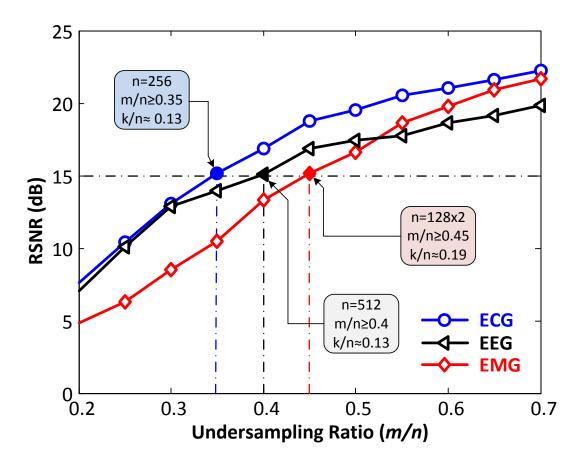

| 7.6  | Die photo and chip summary.                                                                                            | 95 |

| 7.7  | Measured RSNR performance of ECG, EMG, and EEG signals reconstructed                                                   |    |

|      | on DWT, joint DWT-DCT, and DCT basis, respectively.                                                                    | 96 |

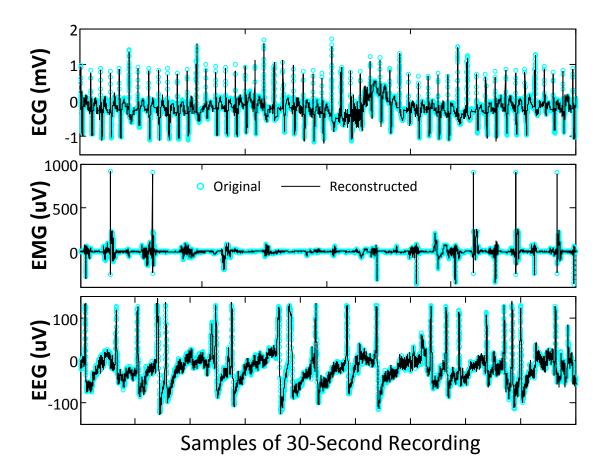

| 7.8  | Examples of the ExG signals reconstructed on the SA engine chip with a $>15$ |     |  |

|------|------------------------------------------------------------------------------|-----|--|

|      | dB RSNR                                                                      | 97  |  |

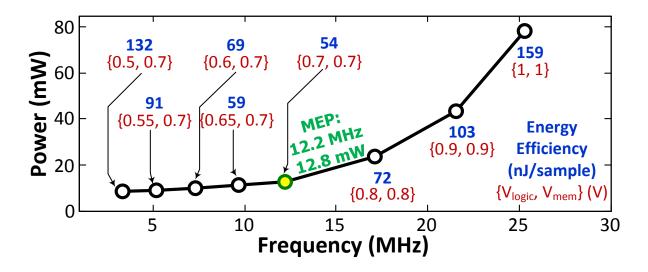

| 7.9  | Measured power versus frequency at different $V_{DD}$ supplies               | 98  |  |

| 7.10 | Measured throughput and energy efficiency of the SA engine chip when         |     |  |

|      | operating at the MEP for ExG signal reconstruction.                          | 99  |  |

| 7.11 | Comparison with an Intel Core i7-4700MQ processor and state-of-the-art chip  |     |  |

|      | implementations of generic SA solvers.                                       | 100 |  |

# LIST OF TABLES

| 1.1 | Qualitative Comparison of SA and Orthogonal Transformation | 3  |

|-----|------------------------------------------------------------|----|

| 3.1 | Pseudo-Code of the OMP Algorithm                           | 26 |

| 3.2 | Pseudo-Code of the Homotopy Algorithm                      | 29 |

| 3.3 | Pseudo-Code of the IST Algorithm                           | 30 |

| 4.1 | Computations of OMP at Iteration $t$                       | 41 |

| 4.2 | Pseudo-Code of the Reformulated OMP Algorithm              | 48 |

| 4.3 | Computations of the Reformulated OMP at Iteration $t$      | 49 |

| 4.4 | Pseudo-Code of the Hierarchical AS Method                  | 52 |

| 5.1 | User-defined Parameters in the SA Engine Soft-IP           | 71 |

| 6.1 | Implementation Results on FPGA                             | 77 |

#### ACKNOWLEDGMENTS

My sincere and deep gratitude goes to my advisor, Professor Dejan Marković, who has guided my research since 2009. Dejan's extraordinary foresight constantly drives me to keep eyes on real-life problems and has directed my research to bridge theory with practical applications. His exceptional wisdom on refining things has made me understand the power of less and the importance of details, which not only impacted my writing and drawing styles but also improved my presentation skills profoundly. I am also indebted to him for his encouraging support for my academic job hunting.

I am grateful that I had the opportunities to work as intern in leading companies during my graduate study. These experiences are fun and eye-opening. I would like to thank Chih-Tsung Huang and his switch ASIC team in the Data Center Group at Cisco Systems Inc. for helping me understand the fundamentals of local area network and sharing with me their experience in VLSI architecture design and project management. I would also like to express my gratitude to David Garrett and the DSP Microelectronics Group at Broadcom Corporation for giving me the opportunity to participate in the design of state-of-the-art communication chips and connecting me with the world-leading chip designers for research discussions.

The research presented in this dissertation is partially funded by Broadcom Corporation. The chip fabrication is supported by TSMC.

Special gratitude goes to Wenyao Xu, Chia-Hisang Yang, Boyu Hu, Hao Yu, and Chenxin Zhang. The research discussions with them have always been inspiring and fruitful. I am also grateful to my labmates in the Parallel Data Architecture Group at UCLA for their valuable input to my research and their kind help on paper proofreading. In addition, I am very blessed to have a bunch of friends playing regular basketball games together at UCLA. This routine of exercise has helped me better handle the pressure from work both mentally and physically. I will miss the games played with Ningyi Wang, Roy Lee, Yen-Hsiang Wang, Hao Wu, Yafeng Zhang, Hao Xu, I-Ning Ku, and Shen Shen.

Most importantly, I would like to thank my parents and my wife for their endless love and support, which have always been giving me the strength and courage to overcome difficulties.

### Vita

- 2004–2008 B.E. (Electrical Engineering), Zhejiang University, Hangzhou, China.

- 2008–2010 M.S. (Electrical Engineering), UCLA, Los Angeles, California.

## PUBLICATIONS

- J5 F. Ren, C. Zhang, L. Liu, W. Xu, V. Öwall, and D. Marković, "A Square-Root-Free Matrix Decomposition Method for Energy-Efficient Least Square Computation on Embedded Systems, *IEEE Embedded Syst. Lett.*, vol. 6, no. 4, pp. 73-76, Dec. 2014.

- J4 F. Ren, W. Xu, and D. Marković, "A Scalable and Parameterized VLSI Architecture for Compressive Sensing Sparse Approximation, *IET Electron. Lett.*, vol. 49, no. 23, pp. 1440-1441, Nov. 2013.

- J3 F. Ren, H. Park, C.-K. K. Yang, and D. Marković, "Reference Calibration of Body-Voltage Sensing Circuit for High-Speed STT-RAMs, *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 60, no. 11, pp. 2932-2939, Nov. 2013.

- J2 R. Dorrance, F. Ren, Y. Toriyama, A. A. Hafez, C.-K. K. Yang, and D. Marković, "Scalability and Design-Space Analysis of a 1T-1MTJ Memory Cell for STT-RAMs," *IEEE Trans. Electron Devices*, vol. 59, no. 4, pp. 878-887, Apr. 2012.

- J1 F. Ren, and D. Marković, "True Energy-Performance Analysis of the MTJ-Based Logicin-Memory Architecture (1-Bit Full Adder)," *IEEE Trans. Electron Devices*, vol. 57, no. 5, pp. 1023-1028, May 2010.

- C6 F. Ren, and D. Marković, "A Configurable 12-to-237KS/s 12.8mW Sparse-Approximation Engine for Mobile ExG Data Aggregation", Proc. IEEE Inter. Solid-State Circuits Conf., Feb. 2015, to appear.

- C5 R. Dorrance, F. Ren, and D. Marković, "An Efficient Sparse Matrix-Vector Multiplication (SpMxV) Kernel For Sparse-BLAS on FPGAs", Proc. ACM/SIGDA Inter. Symp. on Field-Programmable Gate Arrays, Feb. 2014, pp. 161-170.

- C4 F. Ren, R. Dorrance, W. Xu, and D. Marković, "A Single-Precision Compressive Sensing Signal Reconstruction Engine on FPGAs", Proc. Inter. Conf. on field-programmable Logic and Applications, Sep. 2013, pp. 1-4.

- C3 F. Ren, H. Park, R. Dorrance, Y. Toriyama, C.-K. K. Yang, and D. Marković, "A Body-Voltage-Sensing-Based Short Pulse Reading Circuit for Spin-Torque Transfer RAMs (STT-RAMs)," *Proc. Inter. Symp. on Quality Electronic Design*, Mar. 2012, pp. 275-282.

- C2 H. Park, R. Dorrance, A. Amin, F. Ren, D. Marković, and C.-K.K. Yang, "Analysis of STT-RAM Cell Design with Multiple MTJs Per Access," *Proc. ACM/IEEE Inter. Symp. on Nanoscale Arch.*, Jun. 2011, pp. 32-36.

- C1 R. Dorrance, F. Ren, Y. Toriyama, A. Amin, C.-K.K. Yang, and D. Marković, "Scalability and Design-Space Analysis of a 1T-1MTJ Memory Cell," Proc. ACM/IEEE Inter. Symp. on Nanoscale Arch., Jun. 2011, pp. 53-58.

- P2 D. Marković, and F. Ren, "A Scalable and Parameterized VLSI Architecture for Compressive Sensing Sparse Approximation, U.S. Patent, 20150032990, Jan. 2015.

- P1 K.-L. Wang, C.-K. Yang, D. Marković, and F. Ren, "Body Voltage Sensing Based Short Pulse Reading Circuit, International Patent, WO2013043738 A1, Mar. 2013.

# CHAPTER 1

# Introduction

## 1.1 Background and Scope of The Dissertation

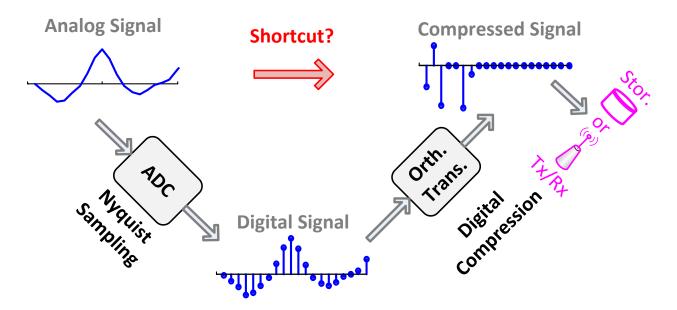

In recent years, compressive sensing (CS) has attracted great research attention in fields of applied mathematics, computer science, and electrical engineering. CS theory is established on the fundamental fact that most natural signals are highly compressible—they can be well represented by only a small portion of their coefficients on a suitable basis [Ca08]. Figure 1.1 shows the Nyquist framework that is the basis of the digital industry today, where an analog signal is first sampled at a high temporal or spatial resolution constrained by the Nyquist frequency. Basically, the Nyquist sampling theorem requires to double the size (sampling rate) of the signal representation in the Fourier basis to avoid information loss. However, most natural signals have very sparse representations on some other orthogonal (non-Fourier) basis. This mismatch implies a large redundancy in Nyquist-sampled data, making compression a necessity prior to storage or transmission (e.g. JPEG-2000, MPEG-4, etc.). From the analog signal to the sparse information of interest (compressed digital signal), the information-acquiring path of the Nyquist framework seems to involve an unavoidable detour. A great question to ask is whether there exists a shortcut or a smarter way of sampling that can bridge the gap between analog signals and sparse information. The answer is compressive sensing.

CS theorems tell us that by performing a linear mapping on the signal with randomness, one is able to well encode the sparse information of a signal with the least amount of redundancy, implying that sampling and compression can be performed at the same time through a compressive sampling process. Interestingly, random encoding is such a powerful

Figure 1.1: Nyquist framework.

scheme that the sparse information can be well preserved regardless of which domain a signal is sparse on. As a result, CS theorems offer us a universal framework for direct data sampling in a compressed format and analog-to-information conversion at a much lower frequency, surpassing the traditional limit of the Nyquist framework. This presents tremendous application values to the data acquisition devices that are sensitive to cost per device, portability, and battery life, especially in mobile and wearable applications.

However, great challenges remain in bringing CS technology into real-life applications. The signal recovery in the CS framework involves solving a sparse approximation (SA) problem, which is an optimization problem of finding the sparest vector from the solution space of a linear or quadratic equation. Unlike orthogonal transformation algorithms used in the Nyquist framework, SA algorithms involve iterative-searching process that leads to high computational complexity and intensive memory access (see Table 1.1). As a result, the software solutions are neither energy-efficient nor cost-effective for real-time processing of compressively-sampled data. For instance, state-of-the-art software solvers running on general computing platforms usually can achieve a real-time processing throughput of 50–500

<sup>&</sup>lt;sup>1</sup>see Section 4.1 for details.

|                                     | $\mathbf{SA}$      | Orth. Trans.           |

|-------------------------------------|--------------------|------------------------|

| Computational Complexity            | $\mathcal{O}(n^3)$ | $\mathcal{O}(n\log n)$ |

| Operational Complexity <sup>1</sup> | High (Iterative)   | Low                    |

| Memory Access Intensity             | High               | Low                    |

Table 1.1: Qualitative Comparison of SA and Orthogonal Transformation

KSamples/s (KS/s) at the power consumption of 10–100 W (see Fig. 7.11). Unfortunately, such performance is a deal-breaker for most real-time CS applications, especially on mobile and wearable platforms, where the target throughput must be achieved very much limited power budgets.

To solve this problem, this dissertation presents a scalable VLSI architecture (the soft-IP core) that can be implemented in reconfigurable logic devices, such as field-programmable gate arrays (FPGAs), or in system-on-chips (SoCs) to perform hardware-accelerated SA for supporting the real-time and energy-efficient signal recovery in CS systems. The soft-IP core is developed in Verilog-HDL. It supports 10 user-specified parameters and can be customized at the compile time, providing the scalability for application-specific user customizations. Taking advantage of the algorithm-architecture co-design based upon the reformulated OMP algorithm, the proposed VLSI architecture features high parallelism, scalability, and configurability, in which all the computing resources are shared for executing the entire algorithm, leading to a 100% utilization of the computing resources.

## 1.2 CS-based Wireless Health Monitoring

Wireless health technology makes medical resources, including medical facilities, medicine and professionals, accessible to anyone, at anytime and anywhere. It enables reducing the medical cost, increasing the engagement between patients and doctors, and promoting connectivity of individuals to the world. The ultimate goal of wireless health is to

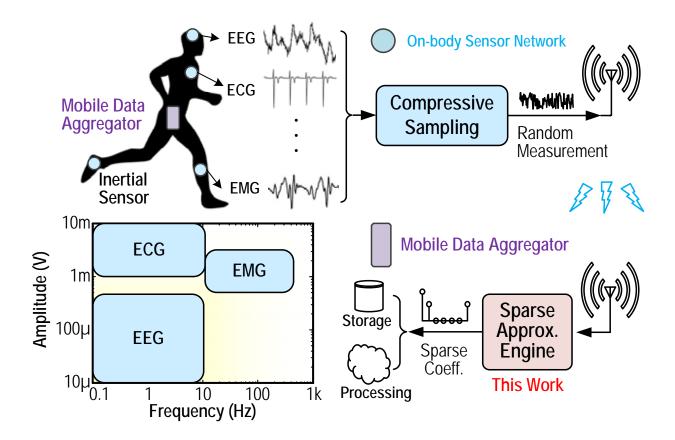

Figure 1.2: A CS-based wireless health monitoring system: always-on sensors compress data for low energy, a mobile data aggregator performs real-time signal reconstruction for timely prediction and proactive prevention.

revolutionize the operation model of the medical system to transform health related services from the system based on episodic examination, disease diagnosis, and treatment to one with continuous monitoring, disease prediction, and prevention [Var07, Xa13]. These changes will make health care systems more effective and economic, benefiting billions of individuals.