Hardware-friendly Deep Learning for Edge Computing

by

Yixing Li

# A Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Approved December 2020 by the Graduate Supervisory Committee:

Fengbo Ren, Chair Sarma Vrudhula Jae-sun Seo Baoxin Li

ARIZONA STATE UNIVERSITY

May 2021

#### ABSTRACT

The Internet-of-Things (IoT) boosts the vast amount of streaming data. However, even considering the growth of the cloud computing infrastructure, IoT devices will generate two orders of magnitude more than the capacity that centralized data center servers can process or store. This trend inevitability calls for the need for offloading IoT data processing to a decentralized edge computing infrastructure. On the other hand, deep-learning-based applications gain great progress by taking advantage of heavy centralized computing resources for training large models to fit increasingly complicated tasks. Even though large-scale deep learning models perform well in terms of accuracy, their high computational complexity makes it impossible to offload them onto edge devices for real-time inference and timely response.

To enable timely IoT services on edge devices, this dissertation addresses the challenge from two perspectives. On the hardware side, a new field-programmable gate array (FPGA)-based framework for binary neural network and an applicationspecific integrated circuit (ASIC) accelerator for natural scene text interpretation are proposed, with the awareness of the computing resources and power constraint on edge. On the algorithm side, this work presents both the methodology of building more compact models and finding better computation-accuracy trade-off for existing models.

#### ACKNOWLEDGMENTS

First and foremost, I am greatly indebted to my advisor, Dr. Fengbo Ren for his consistent guidance, encouragement, inspiration, and support. Dr. Ren motivated me to set a high standard from the beginning of my Ph.D. study, and he also tirelessly shaped me into both an independent researcher and a team player. I have benefited tremendously from his knowledge and experience, and his philosophies about work and life. I would also like to thank my committee members Dr. Sarma Vrudhula, Dr. Jae-sun Seo and Dr. Baoxin Li for their fruitful discussion and guidance over the years.

I would like to thank all PSCLab members: Kai Xu, Michael Riera, Zhikang Zhang, Saman Biookaghazadeh, Erfan B. Tavakoli, Masudul Quraishi and Yuhao Wang for brainstorming together, and all the fun we have had in our lab. Special thanks to my amazing co-authors – Zichuan Liu, Wenye Liu and Shuai Zhang for crosscountry collaborations. I would like to thanks the researchers whoever took a time to give me some comments on my works. Those critical feedback and peer recognition have motivated me to become a better researcher in this Ironman Triathlon.

During the half a year I spent in the industry, I had wonderful intern experience with the guidance of my mentor Dr. Ming Kai Hsu at Cadence Design Systems, and Dr. Xin Lu and Ms. Laurie Byrum at Adobe. I was lucky to work on projects that were highly related to my research background, which allowed me to see the excitement of productizing the research ideas.

I would like to thank my friends for their support throughout the intensive job hunting season during the unforeseen circumstances in current pandemic, especially the accompany and emotional support of my boyfriend, Kun Zhang. Finally, I would like to thank my beloved parents for their understanding and support during the entire Ph.D. journey. This dissertation is dedicated to all of them.

|      |      |         | Pa                                           | age  |

|------|------|---------|----------------------------------------------|------|

| LIST | OF T | TABLES  |                                              | vii  |

| LIST | OF F | IGURE   | S                                            | viii |

| CHAI | PTER | l.      |                                              |      |

| 1    | INT  | RODUC   | CTION                                        | 1    |

| 2    | REL  | ATED    | WORK                                         | 4    |

|      | 2.1  | Neural  | Network Compression                          | 4    |

|      |      | 2.1.1   | Reduce Precision                             | 4    |

|      |      | 2.1.2   | Reduce Connection                            | 6    |

|      |      | 2.1.3   | Other Methods                                | 7    |

|      |      | 2.1.4   | Comparison                                   | 7    |

|      | 2.2  | Hardw   | are Acceleration on the Edge Server          | 8    |

|      |      | 2.2.1   | FPGA Inference Framework for Deep Learning   | 9    |

|      |      | 2.2.2   | ASIC Accelerator for Deep Learning           | 10   |

| 3    | FPG  | GA INFI | ERENCE FRAMEWORK FOR BINARY CONVOLUTION      |      |

|      | NEU  | JRAL N  | ETWORKS                                      | 11   |

|      | 3.1  | Algorit | thm Reformulation for Efficient FPGA Mapping | 11   |

|      |      | 3.1.1   | Binary-encoded Convolution                   | 11   |

|      |      | 3.1.2   | Comparator-based Normalization               | 12   |

|      |      | 3.1.3   | BCNN Model Overview                          | 13   |

|      | 3.2  | Archite | ecture Design and Optimization               | 14   |

|      |      | 3.2.1   | Architecture Overview                        | 14   |

|      |      | 3.2.2   | Architectural Parameters                     | 15   |

|      |      | 3.2.3   | Throughput Modeling and Optimization         | 16   |

|      | 3.3  | FPGA    | Implementation                               | 17   |

# TABLE OF CONTENTS

|   |      | 3.3.1        | PE Unit                                                               | 17 |

|---|------|--------------|-----------------------------------------------------------------------|----|

|   |      | 3.3.2        | Computing Kernels                                                     | 18 |

|   |      | 3.3.3        | Memory                                                                | 19 |

|   | 3.4  | Experi       | imental Evaluation                                                    | 19 |

|   |      | 3.4.1        | Design Environment                                                    | 20 |

|   |      | 3.4.2        | FPGA Implementation Results                                           | 20 |

|   |      | 3.4.3        | FPGA-based Versus GPU-based BCNN                                      | 22 |

|   | 3.5  | Summ         | ary                                                                   | 24 |

| 4 | ASI  | C ACC        | ELERATORS FOR BINARY CONVOLUTION NEURAL                               |    |

|   | NET  | WORF         | κs                                                                    | 26 |

|   | 4.1  | Prelim       | inary                                                                 | 26 |

|   |      | 4.1.1        | Convolutional Encoder-decoder Network (CEDNet) $\ldots \ldots \ldots$ | 29 |

|   |      | 4.1.2        | Binary Convolutional Encoder-decoder Network (B-CEDNet)               | 32 |

|   | 4.2  | Archit       | ecture Design                                                         | 34 |

|   |      | 4.2.1        | Processing Elements                                                   | 35 |

|   |      | 4.2.2        | Memory Design                                                         | 37 |

|   | 4.3  | Datafl       | ow Control                                                            | 38 |

|   | 4.4  | Experi       | imental Evaluation                                                    | 40 |

|   | 4.5  | Summ         | ary                                                                   | 45 |

| 5 | CON  | <b>APRES</b> | S BINARY NEURAL NETWORKS VIA SENSITIVITY ANAL                         | -  |

|   | YSIS | 5            |                                                                       | 46 |

|   | 5.1  | BNN I        | Reconstruction                                                        | 46 |

|   |      | 5.1.1        | Bit-sliced Binarized Input                                            | 46 |

|   |      | 5.1.2        | Non-binary First Layer                                                | 47 |

# Page

|   |     | 5.1.3                   | Binary Constrained Training               |    |  |  |  |

|---|-----|-------------------------|-------------------------------------------|----|--|--|--|

|   | 5.2 | Sensiti                 | ivity Analysis                            | 49 |  |  |  |

|   | 5.3 | Rebuil                  | d a Compact BNN                           | 51 |  |  |  |

|   | 5.4 | Experi                  | imental Evaluation                        | 51 |  |  |  |

|   |     | 5.4.1                   | Experiment on CIFAR-10                    | 53 |  |  |  |

|   |     | 5.4.2                   | Experiment on Other Datasets              | 58 |  |  |  |

|   |     | 5.4.3                   | Runtime Evaluation                        | 60 |  |  |  |

|   | 5.5 | Summ                    | ary                                       | 61 |  |  |  |

| 6 | PRU | JNING                   | BINARY NEURAL NETWORK VIA WEIGHT FLIPPING |    |  |  |  |

|   | FRE | QUEN                    | СҮ                                        | 62 |  |  |  |

|   | 6.1 | Prelim                  | inary                                     | 62 |  |  |  |

|   |     | 6.1.1                   | Iterative Pruning                         | 62 |  |  |  |

|   |     | 6.1.2                   | Optimization-based Pruning                | 63 |  |  |  |

|   | 6.2 | Metho                   | dology                                    | 64 |  |  |  |

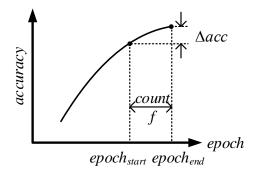

|   |     | 6.2.1                   | Weight Flip Frequency                     | 64 |  |  |  |

|   |     | 6.2.2                   | BNN Compression Flow                      | 66 |  |  |  |

|   | 6.3 | Experi                  | imental Evaluation                        | 68 |  |  |  |

|   | 6.4 | Summ                    | ary                                       | 70 |  |  |  |

| 7 | LIG | HT-WE                   | EIGHT OBJECT DETECTION NETWORKS           | 71 |  |  |  |

|   | 7.1 | Prelim                  | inary                                     | 72 |  |  |  |

|   | 7.2 | Archit                  | ecture Design                             | 75 |  |  |  |

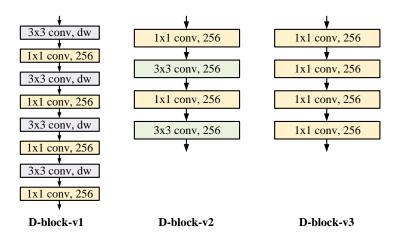

|   |     | 7.2.1                   | Light-weight Block                        | 75 |  |  |  |

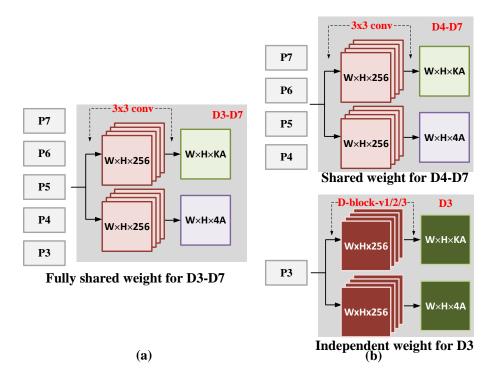

|   |     | 7.2.2                   | Partially Shared Weights                  | 76 |  |  |  |

|   | 7.3 | Experimental Evaluation |                                           |    |  |  |  |

# CHAPTER

|      |      | 7.3.1 | Experimental Setup          | 77 |

|------|------|-------|-----------------------------|----|

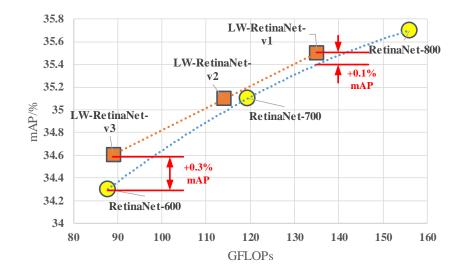

|      |      | 7.3.2 | Performance on COCO Dataset | 78 |

|      | 7.4  | Summ  | ary                         | 81 |

| 8    | CON  | NCLUS | ION AND FUTURE WORK         | 83 |

| REFE | EREN | CES   |                             | 86 |

# Page

| Table | P                                                                            | age |

|-------|------------------------------------------------------------------------------|-----|

| 3.1   | Optimized Parameters for Each Layer                                          | 20  |

| 3.2   | FPGA Resource Utilization Summary                                            | 20  |

| 3.3   | Experiment Results and Comparison                                            | 21  |

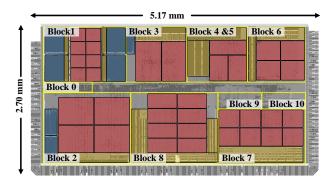

| 4.1   | Memory Summary (Unit:KB)                                                     | 40  |

| 4.2   | Chip Summary                                                                 | 40  |

| 4.3   | Experiment Results and Comparison                                            | 43  |

| 5.1   | Performance Comparison with Different Input Format and $1^{st}$ Layer        |     |

|       | Configuration                                                                | 54  |

| 5.2   | Sensitivity Analysis of Single Bit Slice in Each Channel with Random         |     |

|       | Noise Injected                                                               | 55  |

| 5.3   | Sensitivity Analysis of 1- $N^{th}$ Multiple Bit Slices in Each Channel with |     |

|       | Random Noise Injected                                                        | 56  |

| 5.4   | Performance of CBNNs on CIFAR-10                                             | 58  |

| 5.5   | Performance Results of CBNNs on SVHN, Chars47k, GTSRB and Im-                |     |

|       | ageNet Datasets                                                              | 59  |

| 6.1   | The Layer-wise BNN-pruning Results of the Binarized NIN at Each              |     |

|       | Iteration                                                                    | 68  |

| 6.2   | The Layer-wise BNN-pruning Results of the Binarized AlexNet at Each          |     |

|       | Iteration                                                                    | 69  |

| 6.3   | Experiment Results of BNN Pruning                                            | 69  |

| 7.1   | Comparison Between Different Light-weight Block                              | 79  |

| 7.2   | Configurations of Different Light-weight (LW) RetinaNet                      | 79  |

| 7.3   | Resource Utilization of Intel Arria 10 GX 1150 FPGA Implementation.          | 79  |

| 7.4   | Comparison of Original RetinaNet and Proposed Light-weight RetinaNet.        | 80  |

# LIST OF FIGURES

| Figure | I                                                                                   | Page |

|--------|-------------------------------------------------------------------------------------|------|

| 2.1    | Resource Consumption of $W^{(10,10)} \times A^{(10,10)}$ Multiplication on a Xilinx |      |

|        | Virtex-7 FPGA for Different Architecture                                            | 8    |

| 3.1    | Pseudo Code of the BCNN Algorithm.                                                  | 13   |

| 3.2    | Overview of the Proposed Accelerator Architecture for BCNN                          | 14   |

| 3.3    | Processing Element (PE).                                                            | 18   |

| 3.4    | The Architecture of Computing Kernels and Their FPGA Mapping                        |      |

|        | Schemes.                                                                            | 18   |

| 3.5    | Throughput and Energy Efficiency Comparison with GPU Implemen-                      |      |

|        | tations.                                                                            | 23   |

| 4.1    | Natural Scene Text Interpretation System                                            | 27   |

| 4.2    | Comparison of Different Levels of Natural Scene Text Processing                     | 28   |

| 4.3    | Architecture of the Convolutional Encoder-decoder Network (CEDNet)                  | . 30 |

| 4.4    | Pooling and Up-pooling Layers.                                                      | 30   |

| 4.5    | Architecture of the Binary Convolutional Encoder-decoder Network                    |      |

|        | (B-CEDNet).                                                                         | 32   |

| 4.6    | Architecture of the Binary Convolutional Encoder-decoder Network                    |      |

|        | (B-CEDNet).                                                                         | 35   |

| 4.7    | Processing Elements (PEs)                                                           | 36   |

| 4.8    | BinConv Kernel and Conv Kernel.                                                     | 36   |

| 4.9    | Data Flow Control Between Blocks.                                                   | 39   |

| 4.10   | The Layout of NSTI Accelerator                                                      | 41   |

| 4.11   | Visualization of NSTI Accelerator Output                                            | 42   |

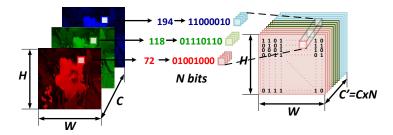

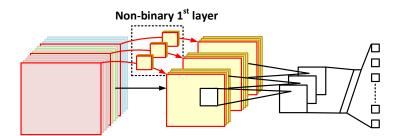

| 5.1    | Conversion from Fixed-point Input to Bit-sliced Binary Input                        | 47   |

| 5.2 | Corresponding Relationship Between Input Bit Slices and Non-binary  |    |

|-----|---------------------------------------------------------------------|----|

|     | First Layer                                                         | 48 |

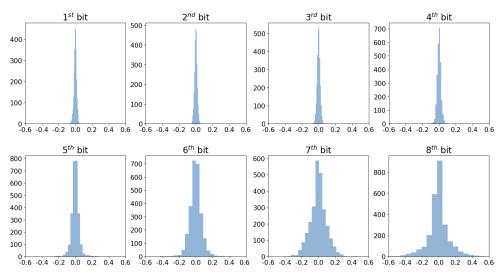

| 5.3 | Histogram of Distributions of Weight Magnitude Associated with Dif- |    |

|     | ferent Input Bits                                                   | 48 |

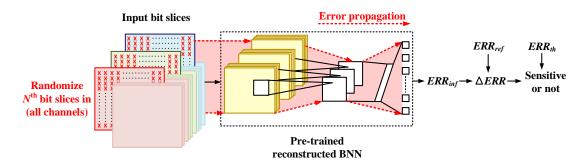

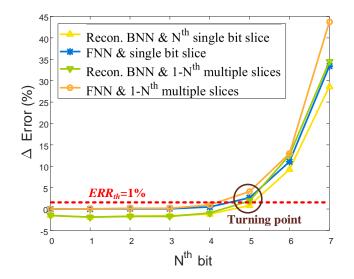

| 5.4 | Sensitivity Analysis of the Reconstructed BNN with Distorted Input  | 50 |

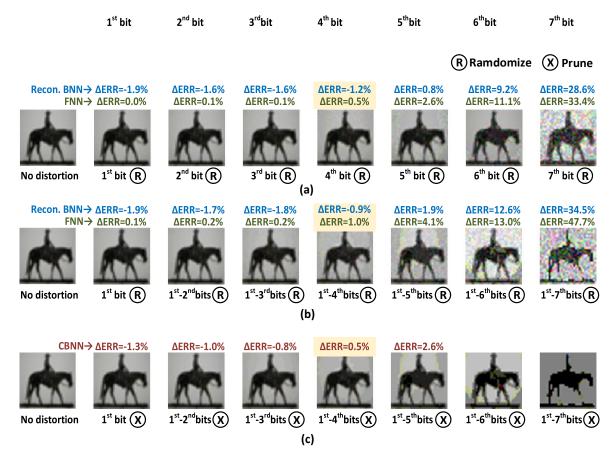

| 5.5 | Visualization of a Horse Image in CIFAR-10 with Different Bit-level |    |

|     | Distortion in Spatial Domain and Frequency Domain.                  | 54 |

| 5.6 | Error Rate of Randomizing One or Multiple Bit Slices in Sensitivity |    |

|     | Analysis.                                                           | 57 |

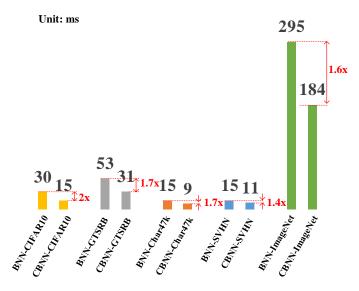

| 5.7 | Runtime Comparison of Different Network Compression Technique       | 60 |

| 6.1 | The Overview of the General Pruning Flow                            | 63 |

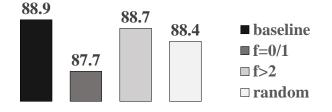

| 6.2 | Accuracy Comparison for Randomizing Different Groups of Weights     | 64 |

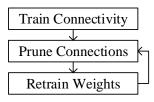

| 6.3 | The Overview of the BNN Pruning Flow                                | 66 |

| 6.4 | The Illustration of Training Interval for $f$ Analysis              | 66 |

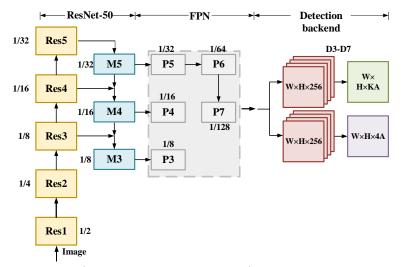

| 7.1 | RetinaNet (ResNet50-FPN-800x800) Network Architecture               | 73 |

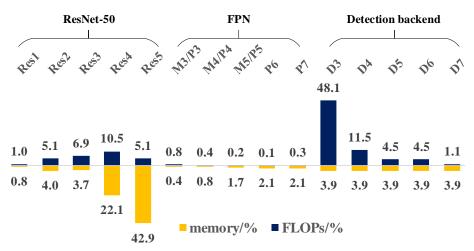

| 7.2 | The FLOPs and Memory (Parameter) Distribution of RetinaNet Across   |    |

|     | Different Blocks.                                                   | 74 |

| 7.3 | Light-weight Blocks for Detection Backend.                          | 75 |

| 7.4 | Fully and Partially Shared Weights for Detection Backend            | 76 |

| 7.5 | FLOPs and mAP Trade-off for Input Image Size Scaling Versus the     |    |

|     | Proposed Method.                                                    | 81 |

#### Chapter 1

# INTRODUCTION

The Internet-of-Things (IoT) boosts the vast amount of streaming data. An estimation of 50 billion IoT devices will be deployed by 2020 (Computing (2016)). In the cloud-based computing scenario, all the data generated by these devices will be stored and processed by the centralized data center servers. However, even considering the growth of the cloud computing infrastructure, IoT devices will generate two orders of magnitude more than the capacity that centralized data center servers can store or process. In addition, due to the latency caused by long server-to-client distance or the network congestion, the recent centralized computing infrastructure is not suitable for any time-sensitive applications. This trend inevitability calls for the need for offloading the IoT data processing to a decentralized edge computing infrastructure (Biookaghazadeh et al. (2018)). On the other side, deep-learning-based applications gain great progress by taking advantage of heavy centralized computing resources for training large models to fit increasingly complicated tasks (LeCun *et al.* (2015)). Even though large-scale deep learning-based models perform well in terms of accuracy, their high computational complexity makes it impossible to offload them onto edge devices or fall for real-time inference and timely response.

To enable more IoT services on edge devices, this work contributes from two critical angles. On the edge device side, a new FPGA-based framework for binary neural network and an ASIC accelerator for natural scene text interpretation are proposed, with the awareness of the computing resources and power constraint on edge. On the algorithm side, this work presents both the methodology of building more compact models and finding better computation-accuracy trade-off points for existing models. The majority of this dissertation has appeared in the following publications.

- Li, Yixing, Zichuan Liu, Kai Xu, Hao Yu, and Fengbo Ren. "A GPU-outperforming FPGA accelerator architecture for binary convolutional neural networks." ACM Journal on Emerging Technologies in Computing Systems (JETC) 14, no. 2 (2018): 1-16.

- Li, Yixing, Zichuan Liu, Wenye Liu, Yu Jiang, Yongliang Wang, Wang Ling Goh, Hao Yu, and Fengbo Ren. "A 34-FPS 698-GOP/s/W binarized deep neural network-based natural scene text interpretation accelerator for mobile edge computing." IEEE Transactions on Industrial Electronics 66, no. 9 (2018): 7407-7416.

- Li, Yixing, Shuai Zhang, Xichuan Zhou, and Fengbo Ren. "Build a compact binary neural network through bit-level sensitivity and data pruning." Neurocomputing (2020).

- Li, Yixing, Akshay Dua, and Fengbo Ren. "Light-Weight RetinaNet for Object Detection on Edge Devices." In 2020 IEEE 6th World Forum on Internet of Things (WF-IoT), pp. 1-6. IEEE, 2020.

- Li, Yixing, and Fengbo Ren. "BNN Pruning: Pruning Binary Neural Network Guided by Weight Flipping Frequency." In 2020 21st International Symposium on Quality Electronic Design (ISQED), pp. 306-311. IEEE, 2020.

This dissertation starts with systematic reviews of the related work of edge device designs and algorithm designs in Chapter 2. The works presented in Chapter 3 and 4 are related to edge computing hardware design. Chapter 3 presents an FPGA-based inference framework, while Chapter 4 presents ASIC accelerators for binary convolution neural networks. Chapter 5-7 are focusing algorithm designs. Chapter 5 and Chapter 6 illustrate two different solutions for compressing binary neural networks. Chapter 7 demonstrates an application-specific solution of light-weight object detection networks for edge computing. Finally, Chapter 8 summarizes the dissertation, and the future works are discussed.

#### Chapter 2

## RELATED WORK

In this chapter, related works for accelerating neural networks on edge are summarized into two categories: neural network compression algorithms and hardware acceleration on the edge server.

2.1 Neural Network Compression

When referring to hardware-friendly oriented designs, it is not fair to only emphasize compressing the network size. Other than that, the computational complexity is also essential. This chapter first discusses and evaluates the related work for network compression by emphasizing both factors. Then a simple benchmark study is presented to help the readers better understand the computational complexity in terms of hardware resource utilization of the existing work. It can reveal why the binary neural network (BNN) is a more superior solution to be deployed on the edge devices.

# 2.1.1 Reduce Precision

BinaryConnect (Courbariaux *et al.* (2015)) is a study in the early stage of exploring the binarized weight neural network. In the BinaryConnect network, the weights are binary values while the activations are still non-binary. Arbitrary value multiplies +1/-1 is equivalent to a conditional bitwise NOR operation. Hence, the convolution operations can be decomposed into conditional bitwise NOR operations and accumulation. It is a big step moving from full-precision multiplication to much simpler bitwise operations.

BinaryNet (Hubara *et al.* (2016)) is the first one that builds a network with both

binary weights and activations. The convolution operation has been further simplified as bitwise XNOR (Exclusive-NOR) and bit count operations. The hardware resource cost is minimized for GPU, FPGA and ASIC implementation. For GPU implementation, a 32-bit bitwise XNOR can be implemented in a single clock cycle with one CUDA core. For FPGA and ASIC implementation, there is no need to use DSP (Digital Signal Processor) resources anymore, which is relatively costly. Simple logic elements – LUTs (Look Up Tables) can be used to map bitwise XNOR and bit count operations, which makes it easy to map highly parallel computing engines to achieve high throughput and low latency.

XNOR-Net (Rastegari *et al.* (2016)) also builds the network based on binary weights and activations. However, it introduces a filter of full-precision scaling factors in each convolutional layer to ensure a better accuracy rate. Additional non-binary convolution operations are needed in each convolutional layer, which cost extra processing time and computing resources.

TernaryNet (Zhu *et al.* (2016)) holds ternary (-1, 0, +1) weights for its network. By increasing the precision level of the weights, it enhances the accuracy rate. Since ternary weights have to be encoded in 2 bits, the computational complexity will at least double, compared with BinaryNet.

LQ-Net (Zhang *et al.* (2018a)) studies the bit-width and accuracy tradeoff between different low-precision configurations. The lower bound of weight and activation precision are constrained to 1 bit and 2 bits, respectively. The bit-width of weight/activation in LQ-Net can be configured to 1/2, 2/2, 3/3, 2/32, 3/32 or 32/32. In this paper, LQ-Net only refers to its most compact version – 1-bit weight and 2-bit activation configuration. Its computational complexity will be the closest one to BinaryNet, while the accuracy is improved, especially for the large networks.

#### 2.1.2 Reduce Connection

Network pruning (Han *et al.* (2015)) is revealed as the most popular technique for compressing pre-trained full-precision or reduced-precision CNNs (weights of the reduced-precision CNN are usually in the range of 8 bit - 16 bit (Suda *et al.* (2016)). It compresses the network by pruning out the useless weights, which gains speedup mainly by reducing the network size. Unlike all the other technique mentioned above, neither the weights nor activations of a pruned network are binary or ternary. Still, the computation complexity of the full-precision or reduced-precision multiply-add operation is much higher than that of the BNN. Overall, different kinds of pruning methods can be categorized as magnitude-based and optimization-based pruning.

For magnitude-based pruning (Han *et al.* (2015)), the key idea is to prune out the weights that have small numerical value, which contribute less to compute the output. In the case of BNN, the weights are constrained to +1/-1, so there is no relative small value weights which can't be applied with magnitude analysis. For optimization-based solution (Carreira-Perpinán and Idelbayev (2018)), the pruned network can be resulted in a non-structured or structured way. For non-structured ones, the prunable weights randomly distributes in the 4-D weight space. In a fullprecision or reduced-precision CNN, the indexes of non-structured prunable weights can be stored in separated masking arrays. The inference speed can be benefited from skipping the computation of masked weights. However, in the case of BNN, since the weights are already in 1-bit data format, the masking array will introduce quite a lot overhead in memory footprint. Besides, additional logic for skipping the computation of masked weights would ruin the pattern of highly paralleled XNOR computations in BNN. The only possible way which can improve runtime performance is to apply optimization-based structured pruning (Zhang *et al.* (2018b); Luo *et al.*  (2017)) on BNN, but no existing work has done any related study. Usually pruning can be applied with 4-8 bit low-precision networks. However, how much redundancy the BNN still has is still unknown, and no existing solution has been proved to work effectively on such compact BNN.

## 2.1.3 Other Methods

Singular Value Decomposition (SVD) is one method that has been applied to BNN to compress its weight matrices (Lin *et al.* (2017a)). The basic idea is to decompose a matrix into lower rank matrices without losing much of the important data. SVD is able to provide high compression ratio for high rank matrices. However, for low-rank binary weight matrices of BNN, SVD can only bring 17% memory saving according to Lin *et al.* (2017a).

#### 2.1.4 Comparison

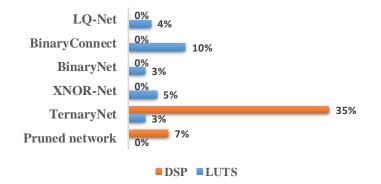

A  $W_{(10,10)} \times A_{(10,10)}$  matrix multiplication is implemented on a Xilinx Virtex-7 FPGA board for analyzing the computational complexity of the different architecture that mentioned above. The precision of elements in W and A are the same as the precision of weights and activations in each architecture. The matrix multiplication is fully mapped onto the FPGA. In other words, the proposed design doesn't reuse any hardware resource. So the resource utilization is a good reflection of computational complexity. Since 16 bits are enough to maintain the same accuracy rate as the full precision network (Suda *et al.* (2016)), the precision of any full precision weights or activations are set to be 16 bits. For the pruned network, 84% of the elements in Wof the pruned network are set to zeros for a fair comparison. (Since pruned network can get up to 13x reduction (Han *et al.* (2015)) while BNN can get 32x, the size of the pruned network is 32/13=2.5x larger. With 16-bit weights, the total number

**Figure 2.1:** Resource Consumption of  $W^{(10,10)} \times A^{(10,10)}$  Multiplication on a Xilinx Virtex-7 FPGA for Different Architecture

of non-zero weights of the pruned network is 2.5/16=16% of that of the binarized weight cases.) For LQ-Net (Zhang *et al.* (2018a)), this work only refer to its most compact configuration in this paper, which has 1-bit weights and 2-bit activations. As shown in Fig. 2.1, BinaryNet and LQ-Net apparently consumes the least amount of hardware resource among all these architecture.

In summary, for all the methods mentioned above, pruning can be categorized as connection reduction, while the rest can be categorized as precision reduction. However, both kinds of methods cannot be applied to the BNN. Regarding to the incompatibility of pruning, detailed explanation has been made in Chapter 2.2. For precision reduction, BNN has already reached the lower bound.

#### 2.2 Hardware Acceleration on the Edge Server

The FPGAs, GPUs, ASIC and other special-purpose chips are designed to help resource-constrained, x86-based devices process large volumes of image or audio data through one layer after another of analytic criteria so the app can correctly calculate and weight the value of each.

For ASIC-based edge accelerators, Apple, Qualcomm and Huawei have all an-

nounced that on-device neural processing engine, aiming at partially moving their AI processing module on device. For GPU-based edge accelerators, Nvidia's Jetson series are designed for power-efficient edge computing with 7.5W power budget.

In this chapter, the discussion is only regarding the related work of FPGA- and ASIC-based accelerators, which generally are one order of magnitude more energy efficient then the GPU ones.

## 2.2.1 FPGA Inference Framework for Deep Learning

Thus far, GPU-based CNN accelerator is still dominant due to its improved throughput over CPUs. However, the high power consumption of GPUs has brought up cooling concerns in data center computing. On the other hand, FPGA-based CNN accelerator has been widely investigated due to its energy efficiency benefits. As the system throughput is proportional to the computing parallelism and operating frequency, the theoretical throughput of GPU-based and FPGA-based CNN accelerators can be estimated on the 1st order based on device specifications. A Titan X GPU has 3,072 CUDA cores, while a Virtex-7 FPGA has 3,600 DSP48 slices. For implementing a full-precision CNN, the computing parallelism of GPUs and FPGAs can be approximately the same. But, GPUs offer 5-10x higher frequency. As a result, FPGAs can hardly match up the throughput of GPUs for accelerating full-precision CNNs. Differently, for a BCNN, the operations in the convolution layers become bitwise XNORs and bit-count logic. A direct impact is that one can use LUTs instead of DSP48 slices to implement the bitwise operations on an FPGA. Hundreds of thousands of LUTs make it possible for a high-end FPGA to match up or surpass the throughput of a GPU, even considering the bitwise operation capability of CUDA cores. Moreover, FPGAs benefit from much higher energy efficiency, which makes it a superior solution for accelerating BCNN in a data center setting. Early research effort (Hubara *et al.* (2016)) shows that GPU can get 7x speedup using a binary kernel for MNIST classification task on a binary multilayer perceptron (MLP). However, there have been very few studies on exploring FPGA-based accelerator architecture for binary neural networks.

## 2.2.2 ASIC Accelerator for Deep Learning

The architecture of ASIC accelerator for general NN acceleration is highly depends on the numerical precision. For CNNs with 8-32 bits, the dominant solution is the systolic array (Jouppi *et al.* (2017)). The layout pattern of processing elements (PEs) is a regular 2-D grid, which alleviates the routing issue and results in relatively high frequency range. For CNNs with lower numeral precision (1-3 bits), the most common solution is to design several general PEs for different kinds of layers. In the case of an ASIC accelerator for BNNs, it has three kinds of computing kernels in hardware: floating-point convolution, binary convolution and fully-connected kernels (Zhao *et al.* (2017)). Since it can only maps a single layer of the BNN at a time, only one kind of computing kernels is active at a time. Such a time multiplexing scheme limits the system throughput due to the low hardware utilization.

Beside the ASICs that designed for general CNN acceleration, there are also designs aiming at specific tasks, e.g. pedestrian detection and etc. In general, different tasks are associated with different NN architecture. A dedicated ASIC design can be tailored for a specific NN architecture and its dataflow. Another key point is, the exciting general NN ASIC accelerator may not support its architecture or dataflow control. A dedicated is needed in this case.

#### Chapter 3

# FPGA INFERENCE FRAMEWORK FOR BINARY CONVOLUTION NEURAL NETWORKS

FPGA-based hardware accelerators for convolutional neural networks (CNNs) have obtained great attention due to their higher energy efficiency than GPUs. However, it is challenging for FPGA-based solutions to achieve a higher throughput than GPU counterparts. In this chapter, an optimized FPGA accelerator architecture tailored for bitwise convolution and normalization that features massive spatial parallelism with deep pipeline stages (Li *et al.* (2018)) are proposed. A key advantage of the FPGA accelerator is that its performance is insensitive to data batch size, while the performance of GPU acceleration varies largely depending on the batch size of the data.

# 3.1 Algorithm Reformulation for Efficient FPGA Mapping

#### 3.1.1 Binary-encoded Convolution

When training the BCNN in (Hubara *et al.* (2016)), the weights and activations are constrained to either +1 or -1. For efficient FPGA mapping, +1/-1s is encoded as 1/0s in the proposed design. In this way, it only takes 1 bit to store a weight or an activation value. Moreover, the convolution operation in layer l is simplified into an XNOR dot product of the input feature map  $a_{l-1}^b$  the weight  $a_l^b$ , given as

$$y_l(x, y, z) = XnorDotProduct(a_{l-1}^b, a_l^b)$$

(3.1)

Equation (3.1) sums up 1s and 0s, which is different from the original BCNN that sums up -1s and +1s. The relation between the original output feature map  $y_{l0}$  and the revised  $y_l$  in the proposed design can be expressed as

$$y_{l0} = 1 \times y_l + (-1) \times (cnum_l - y_l) = 2y_l - cnum_l, \qquad (3.2)$$

where is the total number of bitwise XNOR operations needed for each  $y_{l0}$ . The difference between  $y_{l0}$  and  $y_l$  compensated in the normalization module in the proposed design.

Note that all the layers take the binary feature map of its previous layer as the input except for the first layer. In the proposed design, the input data is rescaled within the range of [-31,31] and use a 6-bit fixed-point data format, which helps to reduce the resource utilization of non-binary operations at the cost of a limited classification accuracy loss of <0.5%.

Since the input image size is  $3 \times 32 \times 32$ , the computational complexity of the first layer is not a dominating factor. The fixed-point dot product of a 6-bit signed input  $a_0$  and a 2-bit signed weight  $w_1$  is denoted as

$$y_l = FpDotProduct(a_0, w_l) \tag{3.3}$$

# 3.1.2 Comparator-based Normalization

The parameters subject to training can be considered as constant values in the inference stage. Therefore, the binarization in (4), the normalization function in (2) and the value compensation in (6) are combined into a modified sign function defined as

$$NormBinarize(y_l, c_l) = \begin{cases} 1, y_l \ge c_l \\ 0, y_l < c_l \end{cases}$$

(3.4)

where  $c_l$  is a constant threshold derived by  $c_l = (cnum_l + \mu - \beta \sqrt{\sigma^2 + \epsilon}/\gamma) \times 0.5$ , and it is rounded to the nearest integer for hardware implementation. The impact of the {1. The first layer}  $y_1 \leftarrow FpDotProduct(a_0, w_1)$   $a_1 \leftarrow NormBinarize(y_1, c_1)$ {2. Remaining hidden layers} for l = 2 to 8 do  $y_l \leftarrow XnorDotProduct(a_{l-1}^b, w_l^b)$ If (l = 2,4,6) then  $y_l \leftarrow MP(y_l)$ end if  $a_l \leftarrow NormBinarize(y_l, c_l)$ end for {3. Output layers}  $y_l \leftarrow XnorDotProduct(a_{l-1}^b, w_l^b)$  $a_l \leftarrow Norm(y_l, c_l)$

Figure 3.1: Pseudo Code of the BCNN Algorithm.

proposed reformulation on hardware implementation is that both the reformulated normalization and binarization functions can be efficiently implemented as a single LUT-based comparator. In addition, one only needs to store one threshold value  $c_l$ for each output value rather than a set of training parameters  $\mu$ ,  $\sigma^2 \beta$  and  $\gamma$ .

# 3.1.3 BCNN Model Overview

The inference flow for the reformulated BCNN algorithm is summarized in Fig. 3.1. The convolution in the  $1^{st}$  layer involves fixed-point dot product operations (FpDot

*Product*), Differently, bitwise XNOR dot product operations (*XnorDotProduct*) are used in all the other layers. Max-pooling (MP) applied in layers 2, 4 and 6. Normalization and binarization are combined as a single function (*NormBinarize*) which is applied in all layers except for the output layer. The output layer ends with the normalization function *Norm* for classification.

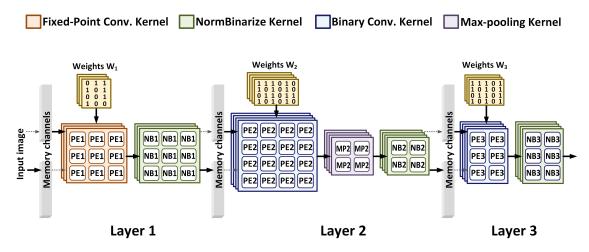

Figure 3.2: Overview of the Proposed Accelerator Architecture for BCNN.

#### 3.2 Architecture Design and Optimization

#### 3.2.1 Architecture Overview

The binary nature of the BCNN enables us to map all the weights, feature maps, and reference values (for normalization) onto the on-chip block RAMs (BRAMs) in a single FPGA. This eliminates any DRAM access latency and dramatically reduces the energy consumption of the system comparing to the existing work relying on offchip storage (Zhang *et al.* (2015); Farabet *et al.* (2011); Qiu *et al.* (2016); Zhao *et al.* (2017)).

Fig. 3.2 shows the overall architecture of the proposed BCNN accelerator. The binary convolutional kernel in each layer is followed by a NormBinarize (NB) kernel with or without a Max-pooling (MP) kernel. All of the kernels are highly parallelized with an optimized number of processing elements (PEs) and operate in a single instruction multiple data (SIMD) fashion. A streaming architecture is enabled by using doublebuffering-based memory channels to handle the data flow between adjacent layers. Each PE in the binary convolutional kernel handles an XNOR dot product operation, which is the core operation in both convolutional and fully-connected layers. The PEs interface with the BRAMs in parallel to read the weights concurrently.

#### 3.2.2 Architectural Parameters

(I) Loop Unrolling. Note that the three nested loops that accumulate the XNOR output values along the three dimensions of a convolutional filter has loopcarried data dependency. Unrolling data-dependent loops is the same as architectural unfolding, which will improve throughput by increasing the level of temporal parallelism. This trades off more hardware resource with improved computing parallelism. The unfolding factor is a critical architectural parameter in the proposed design, denoted as UF. UF has a maximum value of  $WID \times HEI \times DEP$  in each layer.

Differently, the calculation of the pixel values along the three dimensions of an output feature map has no loop-carried data dependency. Unrolling independent loops is equivalent to creating spatial parallelism in the architecture to improve throughput. In the proposed design, the independent loops are fully unrolled to maximize the throughput. The unrolling factor of independent loops is denoted as P. Maximizing P generates a massively parallelized PE array by utilizing the abundant LUT resources on the FPGA.

(II) Pipelining. Loop pipelining is applied in the proposed architecture to further enhance the temporal parallelism and maximize the system throughput. Note that the queuing time to feed in the next data is the inversely proportional to throughput, which is referred to as initial interval I in this chapter. If there is a loop existing in the data path, the minimum initial interval will be limited by the loop latency of the recursive architecture. With loop pipelining, the next data can be feed whenever possible with the minimum initial interval. In the case of a fully pipelined implementation, new data comes in every clock cycle (l=1).

#### 3.2.3 Throughput Modeling and Optimization

If only one XNOR operation and one accumulation are performed in each clock cycle, the total execution time  $Cycle_{conv}$  clock cycles of a convolutional layer can be model as

$$Cycle_{conv} = WID \times HEI \times DEP \times FW \times FH \times FD$$

(3.5)

where WID, HEI, and DEP denotes the width, height, and depth of a convolutional filter, and FW, FH, and FD denotes the width, height and, depth of an output feature map, respectively. When architectural unfolding is applied in performing the XNOR dot product operation in each PE, will be divided by UF. Similarly, when spatial parallelism is applied to create PE arrays for processing P output pixels in parallel,  $Cycle_{conv}$  will be further reduced by P times. The same PE array is reused to calculate the output feature maps with pipelining applied, which contributes to an I-cycle initial interval for the most inner loop. Thus, the throughput of the convolutional kernel with architectural optimization can be formulated as

$$throughput = max(C_1, C_2, C_3, ..., C_k).$$

(3.6)

where freq is the system frequency. Note that  $throughput_{conv}$  proportional to the estimated cycle count  $Cycle_{est}$  convolutional layer, defined as

$$Cycle_{est} = \frac{Cycle_{conv}}{UF \times P} \times I.$$

(3.7)

In the proposed accelerator architecture, a double buffering scheme is used to further enhance the spatial parallelism of the system as shown in Fig. 4. The computation of each layer is triggered at the same time and alternates between two phases. Specifically, one channel of  $fmap_{L-1}$  is used as the input of the  $L^{th}$  layer while the  $L - 1^{th}$  layer is writing new outputs into the other  $fmap_{L-1}$  channel. When both layers finish processing, the memory buffers swap, and the next processing phase is triggered. Therefore, the overall system-level throughput can be formulated as

$$throughput = \frac{max(C_1, C_2, C_3, ..., C_k)}{freq},$$

(3.8)

where  $C_L$  is the execution time of the  $L^{th}$  architecture.  $C_L$  can be either  $Cycle_{est}$ throughput modeling or  $Cycle_r$  evaluating real execution throughput. One should note that the system throughput can be maximized with the optimal hardware utilization when all the layers have equal execution time  $(C_1 = C_2 = C_3 = ... = C_k)$ . In the case that the  $L^{th}$  layer has longer execution time than other layers, one can always increase the parallelism of the  $L^{th}$  layer while decreasing that of other layers to gain throughput with minimum overhead in resource usage. Since the convolutional layers take up over 95% of the computation, only the optimization of convolutional layers is emphasized in this chapter. The fully-connected layer can be easily optimized to match up the system throughput using the same principle.

#### 3.3 FPGA Implementation

In this chapter, it presents the strategy of mapping different computing units to maximize the FPGA resource utilization.

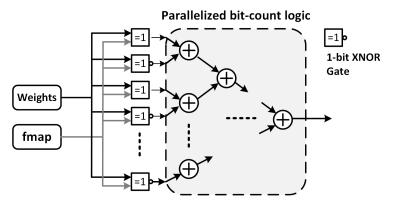

# 3.3.1 PE Unit

The block diagram of a PE unit is shown in Fig. 3.3. A PE unit handles the XNOR dot product operation of a weight vector and a feature map vector from the previous layer. The vectors are fed into an array of 2-input XNOR gates followed by a parallelized bit-count logic for accumulation. Since both the XNOR gates and the bit-count logic take binary values as input, the PEs can be efficiently implemented using the abundant LUT resources. This is the key to enabling massive computing

Figure 3.3: Processing Element (PE).

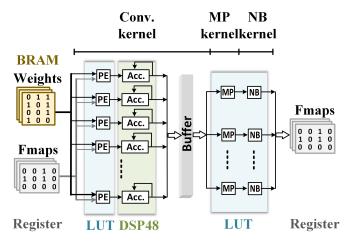

Figure 3.4: The Architecture of Computing Kernels and Their FPGA Mapping Schemes.

parallelism on an FPGA. Note that the number of XNOR gates in each PE is the same as the unfolding factor UF of the current layer. By accumulating the PE output, the pixel value of an output feature map can be computed by the bit-count logic.

# 3.3.2 Computing Kernels

Fig. 3.4 shows the architecture of the convolutional kernel followed by the Maxpooling and NormBinarize kernels. Each convolutional kernel has an array of PEs implemented using LUTs followed by an array of accumulators implemented using DSP48 slices. The number of PEs and DSP slices is equal to the spatial parallelism factor P. Each convolutional kernel thereby computes P pixel values of the output feature map in parallel. Besides the weight arrays, only intermediate results of the accumulator outputs (bit-count results) within a single feature map are stored in BRAMs. Feature maps are mapped onto distributed RAMs.

For the convolutional layers 1, 3 and 5 without max-pooling, the outputs of accumulators are directly connected to the NB kernels. The hardware kernel of fullyconnected layers is similar to Fig. 3.4. Note that the max-pooling is performed in pipeline with the computation of feature maps in the proposed implementation.

# 3.3.3 Memory

To read and write a large number of bits in the same clock cycle, one has to partition and reshape the memory arrays in the BCNN model. Partition essentially breaks down a large data array into smaller ones to fit in multiple BRAMs for parallel access. Reshaping basically redefines the depth and width of a single BRAM by grouping multiple words into a wider one. In the proposed design, the weight and fmap arrays are mapped onto BRAMs and distributed RAMs (registers), respectively. Since the maximum word length of a BRAM in a Virtex-7 FPGA is limited to 32 bits, the weight array first was reshaped by 32 and then was partitioned into several BRAMs to guarantee enough memory bandwidth for the required system throughput.

#### 3.4 Experimental Evaluation

The proposed accelerator architecture is implemented for the BCNN in (Hubara et al. (2016)) using the optimal architectural parameters shown in Table 3.1. UFand P are optimized for making  $Cycle_{est}$  layer approximately the same based on the throughput model in Eq. 3.8. Each layer is also fully pipelined with an initial interval of I = 1. Note that the operations along the FW and the FD dimensions are fully

| Layer  | UF   | Р  | Cycle <sub>conv</sub> | Cycle <sub>est</sub> | Cycle <sub>r</sub> |

|--------|------|----|-----------------------|----------------------|--------------------|

| Conv 1 | 27   | 32 | 3538944               | 4096                 | 5233               |

| Conv 2 | 384  | 32 | 150994944             | 12288                | 12386              |

| Conv 3 | 384  | 16 | 75497472              | 12288                | 12296              |

| Conv 4 | 768  | 16 | 150994944             | 12288                | 13329              |

| Conv 5 | 768  | 8  | 75497472              | 12288                | 12386              |

| Conv 6 | 1536 | 8  | 150994944             | 12288                | 14473              |

Table 3.1: Optimized Parameters for Each Layer

Table 3.2: FPGA Resource Utilization Summary

| Resource      | LUTs   | BRAMs | Registers | DSP   |

|---------------|--------|-------|-----------|-------|

| Used          | 342126 | 1007  | 70769     | 1096  |

| Available     | 433200 | 2060  | 607200    | 2800  |

| Utilization/% | 78.98  | 48.88 | 14.30     | 39.14 |

unfolded for maximizing the throughput.

#### 3.4.1 Design Environment

C language is used to describe the accelerator architecture. Vivado HLS is used to produce the RTL codes. The Vivado Design Suite is used to map the design onto a Xilinx Virtex-7 XC7VX690 FPGA. The execution time in terms of clock cycles is reported by Vivado HLS and the system frequency is reported by Vivado Design Suite after the implementation stage.

#### 3.4.2 FPGA Implementation Results

As shown in Table 3.1, the real execution time  $Cycle_r$  the synthesis report for each layer is well aligned with  $Cycle_{est}$  by the proposed model in Eq. 3.7. The throughput bottleneck is layer 6 in this case. Running at a system frequency of 90 MHz, the FPGA-accelerated BCNN achieves an image processing throughput of 6,218 frames per second (FPS), which is the highest throughput for the same dataset reported by far. The top-1 accuracy rate is 87.8%, which is only 0.3% lower compared to the software model in Theano.

|           | Device         | Clock<br>(MHz) | Bit-width  | GOPS   | Power<br>(W) | Energy<br>Efficiency<br>(GOPS/W) | Performance<br>Density<br>(GOPS/kLUT) | Latency<br>(ms) |

|-----------|----------------|----------------|------------|--------|--------------|----------------------------------|---------------------------------------|-----------------|

| Farabet   | Virtex 6       | 200            | 16         | 147    | 10           | 14.7                             | 0.98                                  | -               |

| Zhang     | Virtex 7       | 100            | 32 float   | 62     | 18.7         | 3.3                              | 0.14                                  | -               |

| Qiu       | Zynq-7000      | 150            | 16         | 137    | 9.6          | 14.3                             | 0.75                                  | 224.6           |

| Suda      | Stratix-V      | 120            | 8~16       | 117.8  | 25.8         | 4.56                             | 0.45                                  | 262.9           |

| Ma        | Arria-10       | 150            | 8~16       | 645.25 | 21.2         | 30                               | 4.01                                  | 47.94           |

| Zhang     | Intel Xeon     | 200            | 32 float   | 123.48 | 13.18        | 9.37                             | 0.62                                  | 263.27          |

| Zhang     | Arria-10       | 385            | fixed      | 1790   | 37.46        | 47.78                            | 4.19                                  | 35.5            |

| Zhao      | Zynq-7000      | 143            | $1 \sim 2$ | 207.8  | 4.7          | 44                               | 4.43                                  | 5.94            |

| Andri     | YodaNN*        | -              | 1          | 525    | 0.06         | 8600                             | -                                     | -               |

| Jouppi    | Google<br>TPU* | 700            | 8          | 92000  | 40           | 2300                             | -                                     | -               |

| This work | Virtex 7       | 90             | 1          | 7663   | 8.2          | 935                              | 22.4                                  | 0.99            |

Table 3.3: Experiment Results and Comparison

To reduce runtime, a bottom-up design strategy was adopted by synthesizing the proposed design layer by layer in Vivado HLS and implementing the entire system in Vivado Design Suite. The overhead introduced by initialization is negligible. Table 4 shows the resource utilization summary for the entire BCNN implementation. LUTs are used for mapping all the computing kernels, including binary convolution, MP and NB kernels. Feature maps of convolutional layers are mapped onto distributed RAMs result in additional LUT consumption. The BRAM usage is mostly consumed by all the weight matrices. Flip-flops are used for storing feature maps and constructing a deep pipeline. Around 30% of the DSP slices are used by the 1<sup>st</sup> layer to perform fixed-point multiplication. For the rest of convolutional layers, DSP slices are used for accumulating PE outputs as shown in Fig. 3.4.

Existing FPGA-based CNN implementations are compared in Table 3.3. To minimize the impact of different FPGA models on throughput, energy efficiency and performance density defined as throughput normalized to resource utilization are used as the performance metrics for comparison. Compared with the FPGA implementations of floating-point or reduced-precision CNNs, BCNN implementation of this work

achieves  $4-124 \times$  higher GOPS,  $20-283 \times$  better energy efficiency and  $5-160 \times$  better performance density. Even compared with the BCNN implementation in (Zhao et al. (2017)), this work achieves 5× better performance density in terms of GOPS/kLUT. The work in (Zhao *et al.* (2017)) implements three kinds of computing kernels in hardware: floating-point convolution, binary convolution and fully-connected kernels. Since this reference work maps a single layer of the BCNN at a time, only one kind of computing kernels is active at a time. Such a time multiplexing scheme limits the system throughput due to the low hardware utilization. In the proposed design, all the layers of the BCNN are mapped into a streaming architecture with optimized architectural parameters, and the data is flowing throughout the entire architecture in a deep pipeline. Therefore, the kernels are constantly active, and the utilization rate of the hardware resources is high. In addition, (Zhao et al. (2017)) consumes extra power for loading the weights from off-chip memory layer by layer in addition to the FPGA power reported. On the contrary, there is no such overhead in the proposed architecture since the network is fully mapped and trained parameters are stored on chip.

#### 3.4.3 FPGA-based Versus GPU-based BCNN

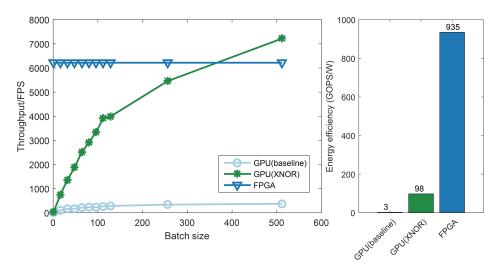

Fig. 3.5 compares the performance of the BCNN accelerated by a Titan X GPU and the proposed FPGA-based design. For GPU acceleration, the baseline kernel is designed for floating-point computation, and the XNOR kernel is optimized for bitwise operations (Hubara *et al.* (2016)). In the XNOR kernel, it concatenates 32 1bit values into a 32-bit value. At the peak performance, each CUDA core can execute 32 bitwise operations per clock cycle. That is the reason why BCNN can also gain remarkable speedup on a GPU when using the XNOR kernel for compilation.

GPU acceleration is apparently sensitive to the size of workload (batch size here).

Figure 3.5: Throughput and Energy Efficiency Comparison with GPU Implementations.

One of the keys to achieving high performance in GPU computing is to hide the long latency of functional units by data-level interleaving especially when there are loopcarried data dependency existed in the algorithm. Only when the workload is large enough, a GPU is able to maintain high thread-level parallelism to achieve a high throughput. Differently, the FPGA-based solution is invariant to the batch size of data. Experiment results show that the proposed design significantly outperforms the GPU acceleration using the baseline kernel in terms of both throughput and energy efficiency. Even compared with the GPU acceleration using the XNOR kernel, which is reported as the best GPU-based CNN performance by far, the proposed design achieves a  $75 \times$  better energy efficiency and an  $8.3 \times$  better throughput for processing data in a small batch size of 16. For processing data in a large batch size of 512 (the maximum size that fit into the GPU memory), the proposed design can match the throughput of the GPU acceleration with a  $9.5 \times$  better energy efficiency.

Therefore, the FPGA-based BCNN solution is a clearly better choice for accelerating the data center applications that process online individual requests in small batch sizes. In a recent study conducted by Baidu, a dominant Internet company in China with 600 million active users, it is reported that the typical on-line prediction workload in terms of batch size is around 8 to 16 (Ouyang *et al.* (2014)). Such small workload is not enough for GPU to achieve its peak throughput performance. Thus, the FPGA-based solution is more superior in handling this kind of requests from individual users.

For processing static data in large batch sizes, the proposed solution is on a par with a Titan X GPU in terms of throughput while delivering much higher energy efficiency. This renders the FPGA-based solution a better choice for energy constrained applications, such as mobile-based advanced driver assistance systems (ADAS). In the ADAS application, a large batch of data needs to be processed for monitoring real-time road condition. In this case, both throughput and energy efficiency are essential and the FPGA-based solution can be deployed.

#### 3.5 Summary

In this chapter, an optimized accelerator architecture tailored for BCNNs is proposed. It is demonstrated for the 1st time that the FPGA-based BCNN solution can greatly outperform a Titan X GPU in terms of both throughput and energy efficiency for processing accurate image classification tasks. The proposed BCNN accelerator running on a Virtex-7 FPGA is 8.3x faster and 75x more energy-efficient than a Titan X GPU for processing individual online requests in small batch sizes. For processing static data in large batch sizes, the proposed solution is on a par with a Titan X GPU in terms of throughput while delivering 9.5x higher energy efficiency. Thus, BCNNs are ideal for efficient hardware implementations on FPGAs regardless of the size of workload. The bitwise operations in BCNNs allow for the efficient hardware mapping of convolution kernels using LUTs, which is the key to enable massive computing parallelism on an FPGA. Applying the optimal levels of architectural unfolding, parallelism, and pipelining based on the proposed throughput model is the key to maximizing the system throughput. Building memory channels across layers with data-flow control is the key to constructing a streaming architecture to further improve the throughput.

#### Chapter 4

# ASIC ACCELERATORS FOR BINARY CONVOLUTION NEURAL NETWORKS

The scene text interpretation is a critical part of the natural scene interpretation. Currently, most of the existing work is based on high-end graphics processing units (GPUs) implementation, which is commonly used on the server side. However, in Internet of Things (IoT) application scenarios, the communication overhead from the edge device to the server is quite large, which sometimes even dominates the total processing time. Hence, the edge computing oriented design is needed to solve this problem. In this chapter, an architectural design and implementation of a natural scene text interpretation (NSTI) accelerator, which can classify and localize the text region on pixel-level efficiently in real-time on edge devices are proposed.

To target the real-time and low-latency processing, the binary convolutional encoder-decoder network is adopted as the core architecture to enable massive parallelism due to its binary feature. Massively parallelized computations and a highly pipelined data flow control enhance its latency and throughput performance. In addition, all the binarized intermediate results and parameters are stored on chip to eliminate the power consumption and latency overhead of the off-chip communication.

# 4.1 Preliminary

Conventionally, text recognition has been vastly investigated for document images (LeCun *et al.* (1998)). However, in the natural scene, the background is much more complicated than that of the document images, which makes the scene text recognition become a more challenging task. With the recent development in neural networks

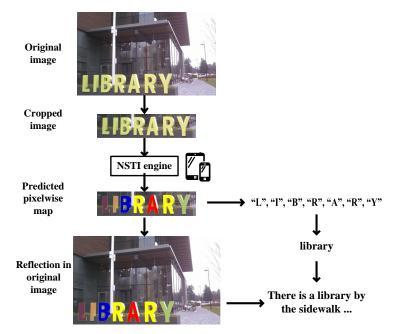

Figure 4.1: Natural Scene Text Interpretation System.

and deep learning (Rahmani *et al.* (2016, 2018)), the accuracy of natural scene text recognition has outperformed the traditional feature selection methods by using features selected automatically The related work can be categorized as character-level based and word-level based solutions. The character-level based solutions (Bissacco *et al.* (2013); Wang *et al.* (2012)) detect and recognize character one at a time. Its front-end is a sliding window approach for character proposals, which makes it suffer from the processing time. The word-level based solution (Jaderberg *et al.* (2014)) requests large fully-connected layer to generate the probability for thousands of word classes, which place a heavy burden on memory access. The shared limitation of either character-level (Bissacco *et al.* (2013); Wang *et al.* (2012)) or word-level based (Jaderberg *et al.* (2014)) solutions is that their architecture is not capable of achieving a low-latency performance. In (Liu *et al.* (2018a)), it performs one-shot text interpretation with a binary convolutional encoder-decoder network (B-CEDNet). Since most of the computation in B-CEDNet are bitwise operations, it opens a new oppor-

Figure 4.2: Comparison of Different Levels of Natural Scene Text Processing.

tunity for hardware acceleration. However, all the previous work mentioned above is implemented by high-end GPUs (such as Nvidia Titan X). The power-hungry highend GPUs are not able to be deployed on energy-constrained mobile devices. If GPUs are deployed on the server side, the communication overhead from a client to a cloud server is quite large, which sometimes even dominates the total processing time. However, long latency is not tolerant in augmented reality (AR) applications. If one chooses to use low-power oriented GPUs, such as Nvidia Tegra X1, on the power constrained edge devices, it will get  $20 \times$  performance (in terms of Flops) degradation compared with the Nvidia Titan X GPU (Inference (2015)). Considering the performance degradation factor, the frame rate in (Liu *et al.* (2018a)) will drop from 200 fps to 20 fps when it is mapped onto a Tegra X1. As such, it cannot maintain a real-time throughput on a lower-power GPU. In addition, the power consumption of a Tegra X1 is 6W (Inference (2015)), which is still too power hungry for a smartphone. Hence, an edge-computing oriented design is needed to solve this problem.

To target a low-latency and real-time processor for energy-efficient natural scene text processing on edge devices, this work propose an ASIC B-CEDNet-based natural scene text interpretation (NSTI) accelerator. As shown in Fig. 4.1, the processor takes the cropped natural scene image as the input and outputs a map of pixelwise classification results with the same size as input. In comparison with generating a bounding box for each character or the entire word (as shown in Fig. 4.2(b) and (c)), the pixelwise classification output (in Fig. 4.2(a)) shows morphological boundary, which is much more user-friendly in AR applications. Compared with binary classification results for the text and non-text regions in Fig. 4.2(d), the proposed processor can identify different characters in a one-shot prediction. In addition, with the localization, morphological and categorized information, it largely alleviates the workload for the back-end word-level prediction and even scene description as shown in Fig. 4.1. The bitwise operation dominated computation in B-CEDNet enables massive parallelism of multiply-add operations (MACs) in the proposed processor. The binarized parameters and intermediate results are fully mapped on chip to eliminate the communication cost (regarding power consumption) instead of loading them from off-chip memory.

In this chapter, the first session discusses the CEDNet architecture for pixelwise interpretation from the algorithm perspective. Then, the second session introduces its binary counterpart, the B-CEDNet architecture. It emphasizes the differences between two architectures and explains how its binary feature brings new opportunity for the hardware acceleration.

## 4.1.1 Convolutional Encoder-decoder Network (CEDNet)

Conventionally convolutional neural networks (CNNs) are used for image classification tasks (LeCun *et al.* (2015); Krizhevsky *et al.* (2012); Goodfellow *et al.* (2016)). Generally, they are composed of convolutional layers, pooling layers, and fully-connected layers [16]. To perform image classification, the network only generates one prediction for the entire image. Therefore, CNNs cannot be directly deployed for the pixelwise interpretation of images. In Fig. 4.3, the convolutional

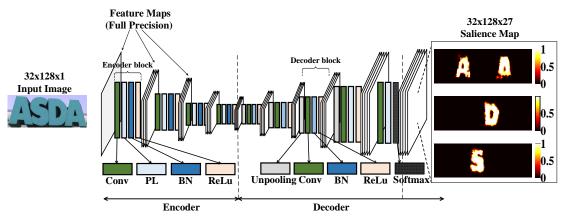

Figure 4.3: Architecture of the Convolutional Encoder-decoder Network (CEDNet).

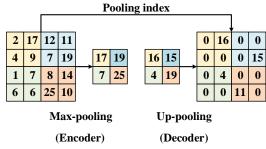

Figure 4.4: Pooling and Up-pooling Layers.

encoder-decoder network (CEDNet) is proposed in (Badrinarayanan *et al.* (2017)) for the multi-class pixelwise classification. A CEDNet takes the scene text images as input. The body of the network can be divided into the encoder part and decoder part. The output of the CEDNet is a salience map  $S \in \mathbb{R}^{W_I \times H_I \times C}$ , which contains the probability information of each pixel over C categories (including one background class), where C is 27 (characters are case insensitive). The encoder part is a stack of encoder blocks, while the decoder is a stack of decoder blocks. Each encoder block contains a convolutional (Conv) layer, a pooling layer (PL), a batch normalization (BN) layer and a rectified linear unit (ReLU) layer. The convolutional layer applies convolutional operations on input feature map  $a_{k-1} \in \mathbb{R}^{W_{k-1} \times H_{k-1} \times D_{k-1}}$  with trainable weight matrix  $w_k \in \mathbb{R}^{w_k \times h_k \times D_k \times D_k}$ , where the subscript k indicates the  $k^{th}$  block. The convolutional operations can be formulated as

$$s_k(x, y, z) = \sum_{i=1}^{w_k} \sum_{j=1}^{h_k} \sum_{l=1}^{D_{k-1}} w_k(i, j, l, z)$$

$$*a_{k-1}(i + x - 1, j + y - 1, l),$$

(4.1)

where  $s_k \in \mathbb{R}^{W_k \times H_k \times D_k}$  is the output of  $k^{th}$  Conv layer. Equation (4.1) shows that the computation of  $s_k$  along three dimensions has no data dependence, which can be highly paralleled in an ASIC implementation. The Conv layer is intended to extract high-level features, which are critical for the pixelwise classification. In the PL layer, it pools out the critical information and eliminates the non-critical one. The PL layer can perform either max pooling or average pooling (LeCun *et al.* (2015)). A max-pooling layer is shown in Fig. 4, it pools out the maximum value in each  $2 \times 2$ window. By introducing the pooling layer, the size of the feature map is shrinking as the network goes deeper. The BN layer is mainly used for accelerating training process (Ioffe and Szegedy (2015)). So in the inference stage, the BN layer is also applied to match the training process forming a stable distribution of the activations  $(a_k)$ . The output of  $k^{th}$  BN layer is represented as follows:

$$a_k(x, y, z) = \frac{s_k(x, y, z) - \mu(x, y, z)}{\sqrt{\sigma^2(x, y, z) + \epsilon}} \gamma(x, y, z) + \beta(x, y, z), \qquad (4.2)$$

where  $\mu$  and  $\sigma^2$  is the mean and variance over the mini-batch training data, while  $\gamma$ and  $\beta$  are trainable scaling factors. The activation function is a nonlinear transformation. The most commonly used activation function (LeCun *et al.* (2015)), ReLU function is represented as

$$a_k(x, y, z) = \begin{cases} 0, a_k(x, y, z) \le 0\\ a_k(x, y, z), a_k(x, y, z) \ge 0. \end{cases}$$

(4.3)

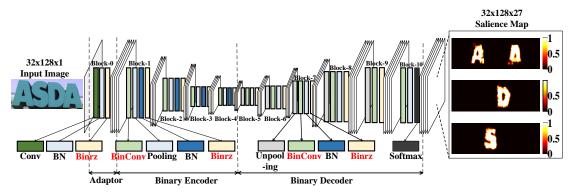

**Figure 4.5:** Architecture of the Binary Convolutional Encoder-decoder Network (B-CEDNet).

The entire encoder part is similar to a CNN without fully-connected layers.

Since the output salience map is desired to be the same size as the input, in the decoder part, each decoder block substitutes the pooling layer with the up-pooling layer. As shown in Fig. 4.4, the up-pooling (UPL) layer pools back the maximum value to the same index in corresponding max-pooling layer. As such, the output salience map can represent the same localized information as the input. In order to predict the pixelwise character appearance probability, the output block replaces the ReLU function with softmax function. As shown in the rightmost part of Fig. 4.3, it only plots the salient map slices for character "A", "D" and "S". The lighter color code means higher confidence level and vice versa. The CEDNet architecture can enable highly parallelized MAC computing inside every encoder or decoder block. It eliminates both the run-time bottle stage in sliding window-based proposal and the computation-intensive fully-connected layer.

#### 4.1.2 Binary Convolutional Encoder-decoder Network (B-CEDNet)

Even though the mobile devices are getting more and more computing power, it is still hard to deploy full-precision CNNs for efficient computing on mobile edge devices. Since the CNN architecture is proved to have huge redundancy (Cheng *et al.*

(2015)), different methods (Courbariaux et al. (2015); Hubara et al. (2016); Rastegari et al. (2016); Han et al. (2015); Jacob et al. (2018)) have been proposed to reduce the computation complexity and/or alleviate the memory access issues. Some approaches (Han et al. (2015)) focus on minimizing total number of parameters, which mainly alleviate the memory access issues. While other approaches (Courbariaux et al. (2015); Hubara et al. (2016); Rastegari et al. (2016); Jacob et al. (2018)) reduce the precision of weights and activations, which can both reduce the computation complexity and alleviate the memory access issues. Among these approaches, binarization (Hubara et al. (2016); Rastegari et al. (2016); Lin et al. (2017d)) can push the weights and activations to be represented in binary format  $w_k^b \in \{0, 1\}^{W_k \times H_k \times D_k \times D_k}$ , and  $a_{k-1}^b \in \{0,1\}^{W_{k-1} \times H_{k-1} \times D_{k-1}}$ . It can achieve up to  $32 \times$  memory saving and converting the convolution operations to bitwise XNOR operations for much more efficient computing. It has been proved in (Liu et al. (2018a)), binarization approach can be adopted in CEDNet to build a binary convolutional encoder-decoder network (B-CEDNet as shown in Fig. 4.5 for pixelwise text classification with merely no accuracy drop.

In the B-CEDNet, it replaces the Conv layer and ReLU layer with the binary convolutional layer (BinConv layer) and Binarization layer (Binrz layer), respectively. The equation for the BinConv layer and Binrz layer is shown in (4.4) and (4.5), respectively.

$$s_k(x, y, z) = \sum_{i=1}^{w_k} \sum_{j=1}^{h_k} \sum_{l=1}^{D_{k-1}} \sim (w_k^b(i, j, l, z)$$

$$\oplus a_{k-1}^b(i + x - 1, j + y - 1, l))$$

(4.4)

$$a_k^b(x, y, z) = \begin{cases} -1, a_k(x, y, z) \le 0\\ +1, a_k(x, y, z) \ge 0 \end{cases}$$

(4.5)

The most costly computation, full-precision multiplication, is now converted into the hardware-friendly bitwise XNOR operation. For GPU implementation, one MAC module can process 32-bit bitwise XNOR instead of one 32-bit multiply-add operation. For FPGA implementation, the BinConv layer is no longer needed to be implemented in DSP slices. Massive LUTs can be used for efficiently implementing bitwise operations. For ASIC implementation, it is flexible enough to build tailored computing units for a BinConv layer with tree-like bitwise XNOR and bit-count logics. With simplified basic computing units, it is able to map massive computing units to target a high system throughput.

B-CEDNet has brought new opportunity in energy-efficient edge-computing applications. Compared with power-hungry GPU-based solutions and overhead of routing in FPGA-based solutions, a tailored ASIC solution for B-CEDNet can be the most energy efficient solution with high throughput performance. It is able to satisfy the need for real-time and low-latency processing in power-constrained edge-computing device for scene text interpretation.

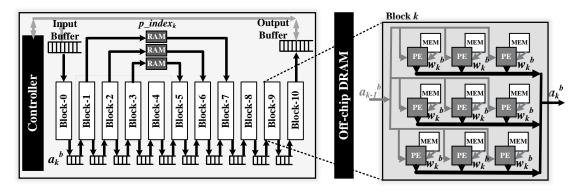

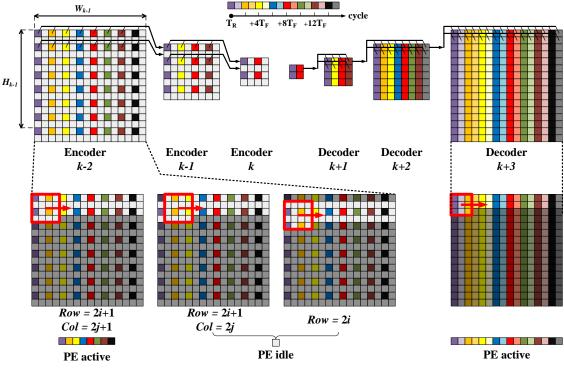

## 4.2 Architecture Design

Most existing ASIC/FPGA-based CNN accelerators are only compatible with encoder blocks (down-sampling trend) for image classification, recognition and detection tasks (Moons and Verhelst (2016); Tu *et al.* (2017)). While some optimized designs for decoder blocks (up-sampling trend) for super resolution applications (Zhang *et al.* (2017)). The proposed architecture is customized for the convolutional encoderdecoder network. The Fig. 4.6 shows the ASIC architecture of the proposed Natural

**Figure 4.6:** Architecture of the Binary Convolutional Encoder-decoder Network (B-CEDNet).

Scene Text Interpretation (NSTI) accelerator. The NSTI accelerator takes the scene text image from the off-chip DRAM as the input. Then it is processed through computing blocks in a streaming manner. The computing blocks, Block-0 to Block-10, are corresponding to 11 blocks in Fig. 4.5. Each computing block is built upon a processing element (PE) array, as shown in the right half of the Fig. 4.6. Each PE performs the operations of convolution, max-pooling/un-pooling, activation function and batch normalization. The spatial parallelism of the NSTI accelerator is reflected on the block level, PE level and sub-PE level. The temporal parallelism is reflected in highly pipelined steaming data flow. Both massive spatial parallelism and temporal parallelism enable high throughput performance of the proposed NSTI accelerator. Reduction in computation complexity to bit-level operations benefits in power saving. Storing all the weights  $(w^b)$  and intermediate results  $(a^b)$  on chip to minimize off-chip communication gives extra credits to energy saving.

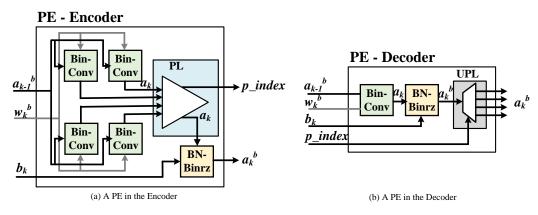

#### 4.2.1 Processing Elements

Each computing block in Fig. 4.6 performs the computation corresponding to Fig. 4.5. Therefore, Block-1 to Block-4 and Block-5 to Block-8 are identical, respectively. Although the functions vary among these blocks, the structure inside each block is the

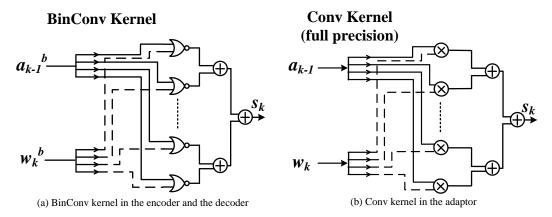

Figure 4.8: BinConv Kernel and Conv Kernel.

same as shown in Fig. 4.6. In each block, PE arrays take the feature map  $a_{k-1}^b$  from previous layers and weight  $w_k^b$  values from its local memory (ROM) as the inputs, and output the feature map  $a_k^b$  of the current layer. All the PEs in the same block work simultaneously. The differences among these blocks exist in their processing elements (PEs).

The PEs of encoder and decoder are shown in Fig. 4.7. The PE of the encoder in Fig. 4.7(a) has 4 BinConv kernels, a PL kernel and a BN-Binrz kernel, while the PE of the decoder in Fig. 4.7(b) has a BinConv kernel, an UPL (un-pooling) kernel and a BN-Binrz kernel. For the convenience of the ASIC implementation, the UPL layer in block k + 1 is grouped with block k for building the computing block. Therefore,

in each decoder PE, it starts with a BinConv kernel and ends with an UPL kernel. If BinConv kernels in an encoder PE are substituted with Conv kernels, it becomes a PE for the adapter. BinConv kernels in Fig. 4.7(a) and Conv kernels of the adapter are both implemented in a tree-like structure as shown in Fig. 4.8. A Conv kernel has a floating-point operation on each node, while a BinConv kernel performs bit-level XNOR and bit-count. They both are implemented by pure combinational logics. In each Conv/BinConv kernel, it computes one  $s_k(x, y, z)$  at a time, that is to say, the parallelism factor in terms of number of operations is  $w_k \times h_k \times D_k$ . The computation of the BN and Binrz layer can be simplified as a threshold function (Li *et al.* (2017)), which can be implemented by a single 2-input comparator, denoted as BN-Binrz kernel in Fig. 4.7. The PL kernel is implemented with a 4-input comparator, which also encodes the index of the maximum value in pooling region. The pooled out value and its index are stored in buffer. Then feed them into the UPL kernel in its symmetric decoder block as shown in Fig. 4.6. The DEMUX in the UPL kernel of Fig. 4.7(b) writes back the (pooled maximum) value with the index information to the right location in the RAM. The up-pooled data in the buffer serves as the input of next decoder block.

## 4.2.2 Memory Design

In DL-based ASIC designs (Chen *et al.* (2017); Desoli *et al.* (2017); Bong *et al.* (2017)), the communication to the off-chip DRAM is very power-intensive. The binary feature of B-CEDNet enable us to store all the weights  $(w^b)$  and intermediate results  $(a^b)$  on chip to minimize off-chip communication for energy saving. As shown in 4.1, the first and second column indicates the memory size of weight values in the non-binary case (CEDNet) and binary case (B-CEDNet), respectively. The total memory size of weights in the B-CEDNet has  $30 \times$  saving, comparing with the non-binary one.